#### EGT0 ENGINEERING TRIPOS PART IA

Monday 11 June 2018 9 to 12.10

## Paper 3

# **ELECTRICAL & INFORMATION ENGINEERING**

Answer all questions.

The *approximate* number of marks allocated to each part of a question is indicated in the right margin.

Answers to questions in each section should be tied together and handed in separately.

Write your candidate number <u>not</u> your name on the cover sheet.

#### STATIONERY REQUIREMENTS

Single-sided script paper

# SPECIAL REQUIREMENTS TO BE SUPPLIED FOR THIS EXAM

CUED approved calculator allowed Supplementary pages: one extra copy of Fig. 2 (Question 1) one extra copy of Fig. 7(a) (Question 6) Engineering Data Book

10 minutes reading time is allowed for this paper at the start of the exam.

You may not start to read the questions printed on the subsequent pages of this question paper until instructed to do so.

# **SECTION A**

## 1 (long)

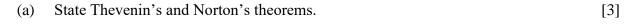

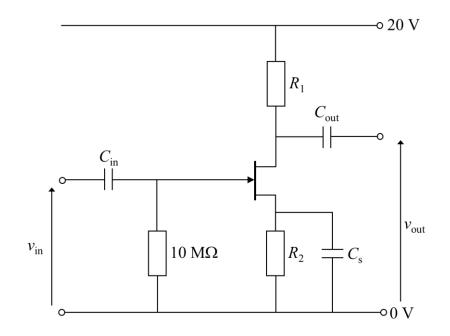

(b) Calculate the Thevenin and Norton equivalents of the circuit in Fig. 1(a). [9]

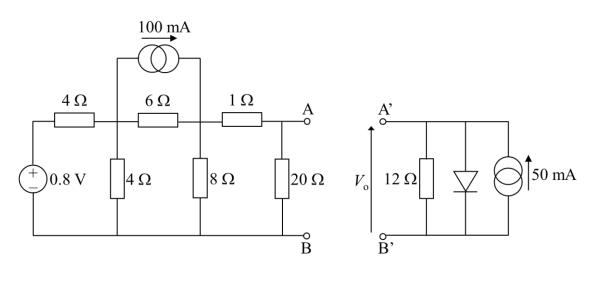

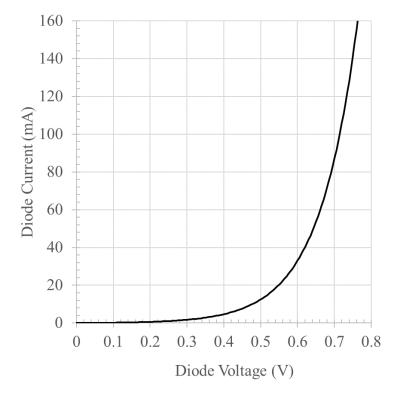

(c) Figure 1(b) shows the equivalent circuit of a solar cell under illumination by sunlight. It consists of a 50 mA ideal current source in parallel with a diode and a 12  $\Omega$  parasitic shunt resistance. If the current–voltage characteristics of the diode are as shown in Fig. 2, calculate the output voltage,  $V_0$ , between the cell's terminals A' and B'. A copy of Fig. 2. is reproduced at the end of this paper for you to detach and hand in with your answer.

(d) The solar cell in Fig. 1(b) is connected to the circuit in Fig. 1(a) by connecting terminal A to terminal A' and terminal B to terminal B'. Calculate the new output voltage  $V_0$  from the solar cell. [9]

Fig. 1(a)

Fig. 1(b)

[9]

Fig. 2

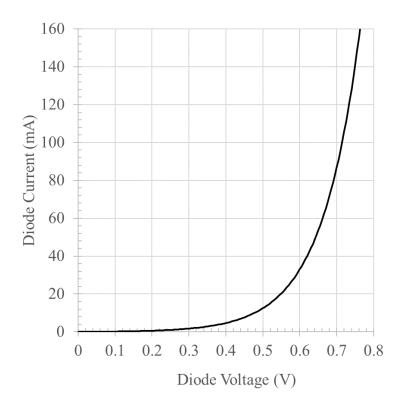

2 (long) Figure 3 shows a field effect transistor (FET) configured in an amplifier circuit. The impedances of  $C_{\rm in}$ ,  $C_{\rm s}$  and  $C_{\rm out}$  are negligible at mid-band frequencies. The circuit is biased so that  $V_{\rm GS} = -2$  V,  $V_{\rm DS} = 10$  V and  $I_{\rm DS} = 1$  mA. At this operating point the small signal parameters of the FET are  $g_{\rm m} = 10$  mA V<sup>-1</sup> and  $r_{\rm d} = 25$  k $\Omega$ .

(a) Explain the purposes of the capacitors

$$C_{in}$$

,  $C_s$  and  $C_{out}$  in the circuit. [2]

(b) Calculate the values for

$$R_1$$

and  $R_2$  to achieve the stated operating point. [6]

(c) For the amplifier circuit of Fig. 3 draw the small signal model for mid-band frequencies. Hence calculate the small signal voltage gain, and the input and output impedances.

[12]

(d) A load of resistance  $R_L = 10 \text{ k}\Omega$  is connected across the output terminals. Assuming that the lower 3 dB cut-off frequency of the amplifier is dominated by the effect of  $C_{\text{out}}$ , what value of  $C_{\text{out}}$  is required if the circuit is to have a 3 dB low-frequency cut-off of 100 Hz? [6]

(e) The previously stated value of the external load resistor  $R_L = 10 \text{ k}\Omega$  does not maximise the power in the load. Calculate a new value of  $R_L$  in order to maximise the signal power in the load. [4]

Fig. 3

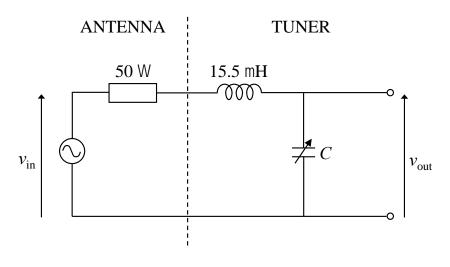

3 (short) Figure 4 shows a radio frequency tuner circuit connected to an antenna. The antenna has an internal resistance of 50  $\Omega$ . The tuner circuit consists of a 15.5  $\mu$ H inductor and a variable capacitor, *C*.

(a) The variable capacitor is adjusted to 3.1 nF. If the antenna produces an r.m.s. voltage  $v_{in}$  of 100 mV at 513 kHz, find the magnitude of the current through the capacitor and its phase with respect to the voltage  $v_{in}$  at the antenna. [6]

(b) Determine the capacitance of the variable capacitor required to tune the circuit to receive BBC Radio Cambridge at 1.026 MHz. [4]

Fig. 4

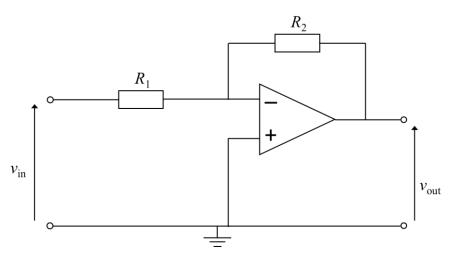

### 4 (short)

(a) For the inverting op-amp circuit of Fig. 5, and assuming the op-amp is ideal, derive an expression for the voltage gain in terms of  $R_1$  and  $R_2$ .

[3]

Fig. 5

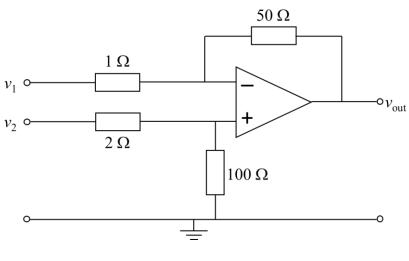

(b) Figure 6 shows the circuit diagram of a difference amplifier. Assuming the opamp is ideal, calculate the voltage gain  $\frac{v_{out}}{v_2 - v_1}$ . [7]

Fig. 6

# Version TH/5

5 (short) A small factory consumes 20 kW of power with a lagging power factor of 0.8 at the factory. When it is connected to the 50 Hz mains power supply, the r.m.s. voltage across the factory terminals is 240 V. The line supplying the factory has an impedance  $Z_s = 0.1 + j0.1 \Omega$ .

(a) Draw a circuit diagram for the above system. Calculate the real power lost in the line.[6]

(b) Assuming that the r.m.s. voltage across the factory terminals continues to be 240 V, calculate the value of the capacitor connected across the factory terminals that is needed to correct its power factor to unity. What is the power lost in the line in this case?

## **SECTION B**

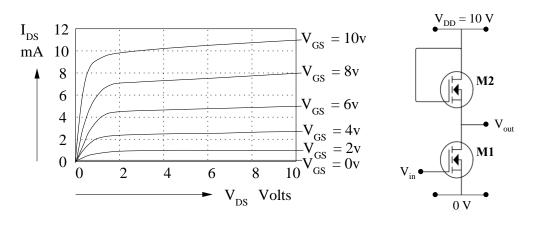

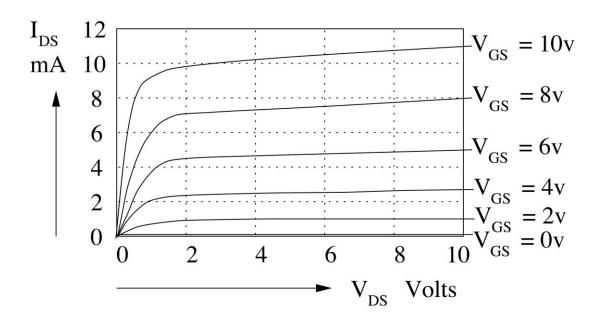

6 (short) The characteristics of NMOS transistors M1 and M2 are shown in Fig. 7(a).

(a) Using the characteristics provided, briefly explain the function of the NMOS transistor M2 in Fig. 7(b). A copy of Fig. 7(a) is reproduced at the end of this paper for you to detach and hand in with your answer.

(b) What is the logic implemented by the circuit in Fig. 7(b)? Explain the drawback of this circuit. [5]

Fig. 7 (b)

7 (short) In a half-adder circuit, two single bit numbers X and Y are added and the result is stored in a two-bit number  $Z_1Z_0$ , where  $Z_0$  represents the least significant bit.

| (a)         | Using a truth table, derive the logic expressions for $Z_1$ and $Z_0$ .                                                                      | [4] |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| (b)<br>requ | If any two-input logic gate can be used, what is the minimum number of gates<br>ired to implement the half-adder? What gates should be used? | [2] |

| (c)         | Implement the half-adder using NAND gates only.                                                                                              | [4] |

8 (short) A 256 kilobyte memory chip has 16 data lines.

| (a) How many address lines does the memory chip have? | [4] |

|-------------------------------------------------------|-----|

|-------------------------------------------------------|-----|

(b) In a microprocessor with 20 address lines, how many of these memory chips can be connected? What are the address ranges of these chips in hexadecimal format? [6]

9 (long) A polymer mixing plant includes a heater (H), an inlet valve (V) and a mixer (M). A synchronous controller system for the plant is to be designed using JK bistables. The system starts from STATE 0, where *H*, *V*, and *M* are turned OFF (H = V = M = 0). It remains in this state until a push button (B) is pressed (B = 1) where the system enters STATE 1, with only H turned ON. Regardless of whether B is pressed or not, the system then moves to STATE 2 where both H and M are OFF and V is ON. Again, regardless of whether B is pressed or not, the system then moved to STATE 3 where both H and Mare ON and V is OFF. If B is pressed while the system is at STATE 3, it returns to STATE 2, otherwise the system returns to STATE 0.

| (a)          | Draw the state diagram of the mixing plant controller system.                                              | [5]  |

|--------------|------------------------------------------------------------------------------------------------------------|------|

| (b)<br>trans | How many bistables would be needed to implement the controller? Draw the state ition table.                | [12] |

| (c)<br>and H | With the aid of Karnaugh maps, develop simplified Boolean expressions for the J K inputs of the bistables. | [8]  |

| (d)          | Draw the complete circuit implementation.                                                                  | [5]  |

#### **SECTION C**

10 (**short**) A metal sphere of radius 20 mm is placed in air with its centre 100 mm vertically above an infinite, horizontal, grounded, conducting plane and the sphere is then charged to 60 V relative to the plane. What is the approximate direction and magnitude of the electric field just above the conducting plane directly under the centre of the sphere? [10]

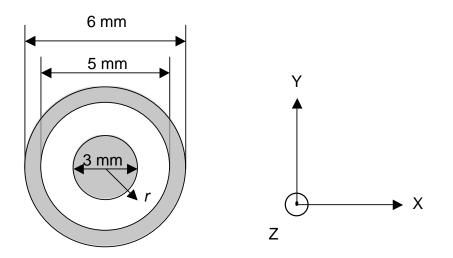

11 (**short**) The cross-section of a coaxial cable, which may be taken to be infinitely long, is shown in Fig. 8. It consists of an inner conductor of diameter 3 mm, and an outer conductor which has an inner diameter of 5 mm and an outer diameter of 6 mm. The conductors are separated by air. The inner conductor carries a constant current of 1.5 A flowing in the positive z direction and the outer conductor carries a constant current of 1.5 A flowing in the negative z direction.

- (a) Sketch the magnetic flux density, showing its direction. [5]

- (b) Calculate the magnetic flux density at radii of 1.5 mm, 2.5 mm and 4 mm. [5]

Fig. 8

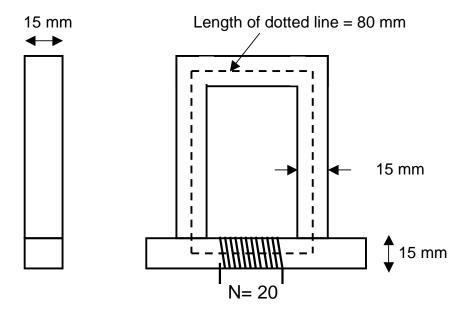

12 (long) (a) A soft iron bar with a square cross-section is placed touching the ends of a C-shaped soft iron bar with a square cross-section, as shown in the side elevation of Fig. 9, in which all dimensions are in mm. The relative permeability of both bars is fixed at 1000. A coil with 20 turns is wrapped around the straight bar. What is the approximate magnetic flux density at the centre of the straight bar if a current of 2 A is passed through the coil? [10]

(b) If the weights of the straight bar and coil are negligible, what is the maximum weight which can be suspended from the straight bar (assuming that it is in contact with the C-shaped bar) without it being pulled from the C-shaped bar? [10]

(c) The straight and C-shaped bar are now separated so that there is a gap of 2 mm between the two. What is the approximate magnetic flux density at the centre of the straight bar now? [10]

Fig. 9

#### **END OF PAPER**

Candidate Number:

### EGT0 ENGINEERING TRIPOS PART IA Monday 11 June 2018, Paper 3, Question 1

Extra copy of Fig. 2 for Question 1

Candidate Number:

EGT0 ENGINEERING TRIPOS PART IA Monday 11 June 2018, Paper 3, Question 6

Extra copy of Fig. 7(a) for Question 6