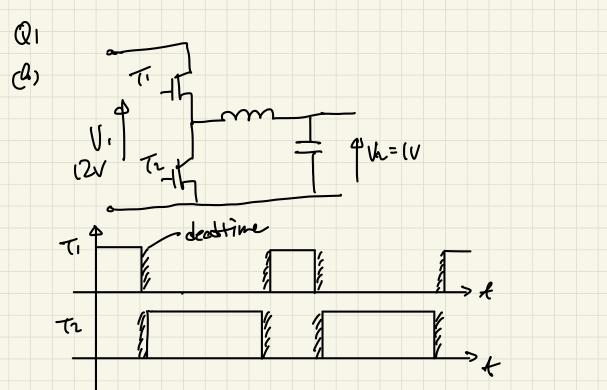

(ط To has borrer switching loss. The borg diale of To conducts connect during deattine. Therefore, When T2 surides on after the deadtime, it has vearly zero where and the suitching on loss is hearly zero.

C) 12 . 12 . 10 . >£ ; <del>'</del>4T Τ -= (V,-16)st DiL SIL = Vi- VL (48-12) × 4 × 1 500×103 = 4. 5×10-6 H  $\Xi$ 4.5 ml 6) <u>lo</u>\_ Ł 0 南 (48-12)×4× 500×c3 (Vi-K)st Dil 1'= -8 = 0.9 uH

(e)  $b = t < \frac{T}{4}$ . To conducting.  $P_{T_1} = \frac{\int_{-T_1}^{T_4} i_{T_1}^2 R dt}{T} = \frac{P_1 \int_{-T_1}^{T_4} (\frac{80}{T} t)^2 dt}{T} = \frac{(85)^2 R}{(\frac{3}{T} t)^2} \frac{t^3}{4} \int_{-T_1}^{T_4} \frac{t^3}{3} \int_{-T_1}^{T_4} \frac{t^3}{3}$

$= \frac{100}{3}R = 0.067W$

$\begin{aligned} \overline{4}c+c < \tau, \quad \overline{72} \quad conducting. \\ \tau \\ \overline{7} \\$

$\frac{1}{Alterathe:} \text{ using Runs Center to that the total$  $<math>loss \cdot P = (\frac{20}{3})^2 \cdot R = 0.267 \text{W}. \quad Pri = \neq P = 0.067 \text{W}. \\ Pri = \neq P = 0.067 \text{W}. \\ Pri = \neq P = 0.287 \text{W}.$

[]

(f) CCM:

I = Ipt + Tripple, Iripple has peak uche 2A

$I_{RMS} = \int I_{RC} + I_{ripple} R_{NS} = \int I_{O}^{2} + \left(\frac{2}{O_{S}}\right)^{2}$

PLOSSCON = JRNSR = (100+4)R

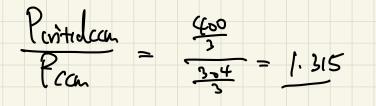

Crittical Ccan

I = Ipct Inpple. Jripple hes perle value coA

$IPNS = \int Ipc + Ipple = \int [0^2 +$  $\left(\frac{10}{10}\right)^2$

$P \left[ oss critical con = \left( \left[ 00 + \frac{100}{3} \right] \right] \right]$

A ALIZIA VO A ALIZIA NA TVO VIII JUIN A ALIZIA VIII A ALIZIA VIIII A ALIZIA ()2. (a) Voc -

b) The copacitor is vong longe thus the DC votige is clamped at the peak voltge of input. Voc = 5 . Varms = 52×230 = 325V. the import current is very distorted so the power factor is poor.

C) Flux is continears, Vo M. D. It's a step down Flyback, this Mi = 1/20  $\frac{D}{1-D} \cdot \frac{1}{20} = \frac{15}{325} \quad D = 0.48$

(d)  $V_{n}$ Ìm  $1 \land \land e$ żp ( 1 >t  $\phi \phi$ / >+ e) Max Bm is set by saturation point  $B_m = 0.75 \times 0.36 = 0.27 T.$ Qu = Bn · A = 0.27 × 0.25×154 = 0.0675×154W  $N_{i}\frac{d\phi}{dt} = V_{in}$  $N_1 = \frac{\Delta + V_{in}}{\Delta \phi} = \frac$ = 46,2 = 46  $N_{2} = \frac{46}{20} = 2.3 \gtrsim 2$

Using the modified turns ration <u>46</u>=23, modified duty rotio  $\frac{p'}{1-D'} = 23 \times \frac{15}{325}$ D'= 0.515  $(\uparrow)$

ASSUM: 9 Bis evenly distributed in the cre 3 Leskye inductore is neglestet.

$\frac{J_{2max} \cdot (I-D)T}{I_2 \cdot T} = \frac{J_2 \cdot T}{I_2 \cdot T}$

$\frac{2}{J_{2NOX} = \frac{2J_{2}}{1-D} = \frac{2\times 2}{1-0.515} = 8.25A.$

Magnetis inductoria referred to 2nd side,  $V_0 = L_m \Delta t$ ,  $L_n = \frac{V_0 \Delta t}{\Delta i 2} = \frac{V_0 (I-D)T}{I_{2000X}}$

= (J × 0.48 × Joxp3 8.25 = 1.76×10-6H

$L_m = \frac{N_n^2 M_s M_s A}{\ell}, \quad M_r = \frac{L_m \ell}{N_r^2 A M_o}$  $= \frac{\left[.76 \times 10^{-6} \times 10^{-2}\right]}{2^{2} \times 0.2 \text{ Tx}} \times \left[.26 \times 10^{5}\right]$ = 139.6

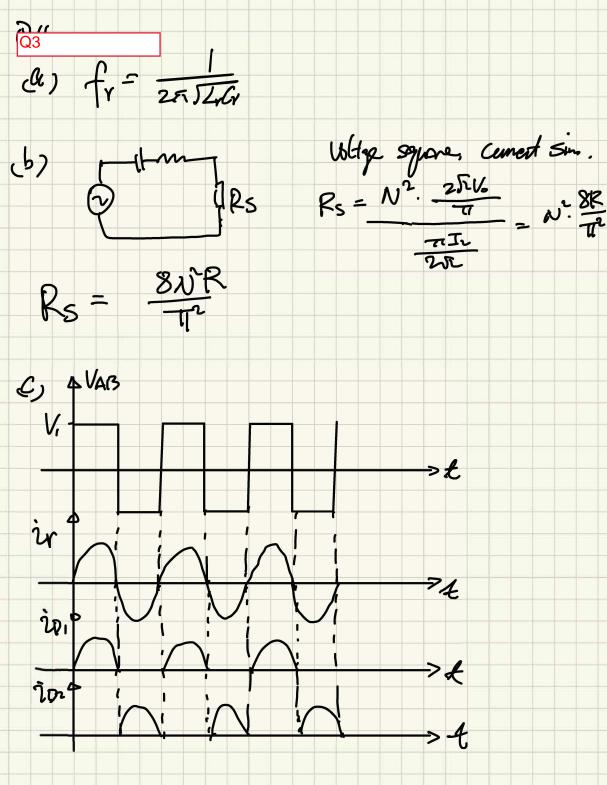

(d) The magnetist inductor of borston is very Onge, At fs, the tank injedoua is zero.  $denfine, V_0 = \frac{V_{ABI}}{N} = \frac{4 V_1}{4 N}$  $l) In this LLC, \ b=\frac{Lm}{Lr} \rightarrow \infty.$ When Q is small, the gain changes insignificantly When for devictes from fr. For a given voted current, the Q can be set to be small. Then, when the Load is reduced Q can only be even smaller. The dard draws the sain is becoming even smoother. Thus the pain hes even smaller changes when fs is not fr. Olerefore, no motter the lood charge, the sain venoists rearly unchanged.

[20%]

Q4

(a)

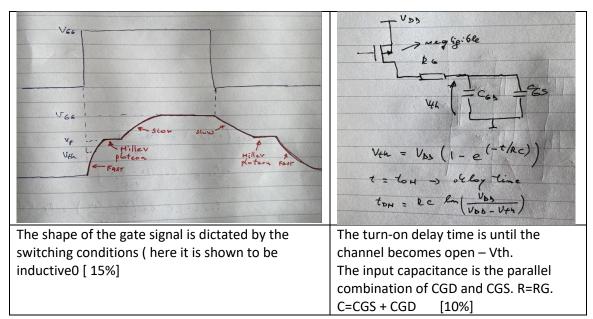

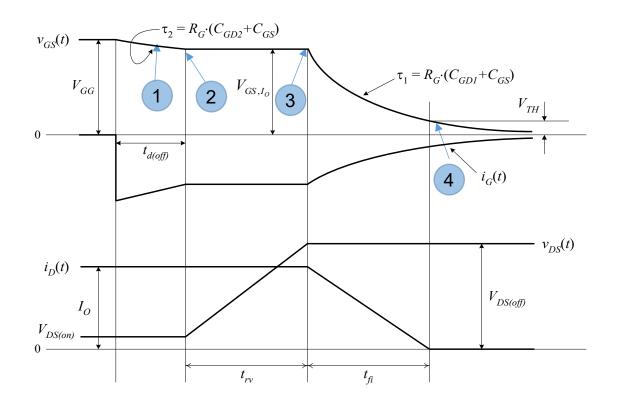

- *C*<sub>*GD1*</sub> Miller capacitance (saturation region this capacitance is small)

- C<sub>GD2</sub> Miller capacitance (linear region –this capacitance is large)

- C<sub>GS</sub> Gate-Source capacitance

- $t_{doff}$  Initial delay time

- $t_{rv}$  Rise time in which  $v_{DS}$  reaches its off-state value  $V_{DS(off)}$  from  $V_{DS(on)}$ .

- $t_{fi}$  Time taken for  $i_D$  to fall from its full load value  $I_O$  to 0; the end of this

[40%]

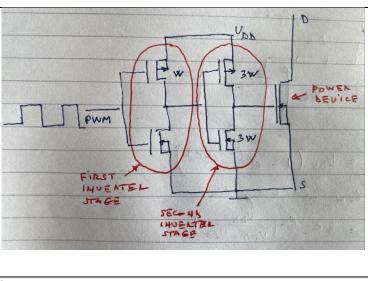

The two-stage inverters are typical CMOS with a n-channel on the low side and p-channel on the high side. The second inverter has larger transistors (e.g. 3x width or even larger) to minimise the on-state resistances of the n-channel and p-channel transistors. The gate resistance is not specifically shown, but could be internal or added between the output of the second stage and the gate of the power transistor to control the dVdt.

[15%]

(b)