1° (a)

$$M = \frac{\sqrt{p_h}}{\sqrt{3/2}} = \frac{\sqrt{3}\sqrt{\sqrt{3}}}{\sqrt{3/2}} = \frac{\sqrt{3}\sqrt{3}\sqrt{3}}{\sqrt{3}} = \frac{2\sqrt{3}}{3}\frac{\sqrt{N_L}}{\sqrt{3}}$$

When non-linear modelstins, the mex phase coltige is a squere wome for the gypon women the fundamental has peak which as  $\frac{4}{\pi}$  of the squere word.

$\sqrt{p_h} = \frac{44}{7}\sqrt{3}c$ ,  $\sqrt{N_L} = \frac{4\sqrt{3}}{7}\sqrt{3}c$ ,  $\sqrt{N_L} = \frac{2\sqrt{3}}{7}\sqrt{3}c$

When non-linear modellatin:  $\sqrt{N_L} < \frac{\sqrt{3}}{2}\sqrt{3}c$

The Smithing frephoney is reduced when non-linear modellation, therefore the Smithing last is reduced.

The harmonics are increased by non-linear modellation.

C)  $\sqrt{N_L} = \frac{3}{10}\sqrt{\frac{3}{10}} = \frac{3\sqrt{3}\sqrt{3}c}{\sqrt{3}c}$

The harmonics are increased by non-linear modellation.

C)  $\sqrt{N_L} = \frac{3}{10}\sqrt{\frac{3}{10}} = \frac{3\sqrt{3}\sqrt{3}c}{\sqrt{3}c}$

The Very  $\sqrt{N_L} = \frac{3\sqrt{3}\sqrt{3}c}{\sqrt{3}c}$

The  $\sqrt{N_L} = \frac{3\sqrt{3}c}{\sqrt{3}c}$

The  $\sqrt{N_L}$

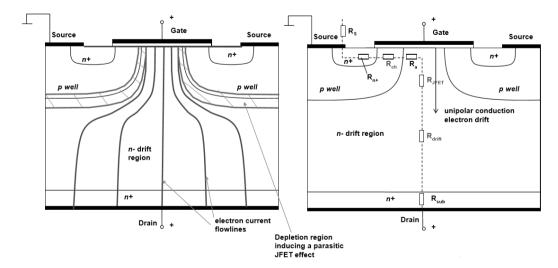

The JFET effect is due to the depletion region expansion in the "neck" region of the power MOSFET – that is the region between two adjacent p-wells. This depletion region is due to the reverse bias of the junctions between p-wells and the drift region, when a positive potential is present on the drain with respect to that of the source potential. The JFET depletion region further narrows down the electron current path within the neck region. This is because the electric field created within each of the adjacent depletion regions pushes the electrons away in the space between the depletion regions.

RDS(ON) is made up of the series combination of all the parts of the device between the source and drain where there is a voltage drop due to the electron current flow. Some of these components are negligible in some voltage ranges. Note that we assume to operate in the linear region of operation of the on-state.

RDS(ON) = Rs + Rn+ + Rch + Ra + RJFET + Rdrift + Rsub

- In general the package resistance Rs, the source resistance Rn+ and the silicon substrate resistance Rsub, are negligible, but their effect in low-voltage, high current devices can still be significant.

- The channel resistance Rch and the accumulation layer resistance Ra, play an important role, especially for the low-voltage devices.

The Rdrift is the drift region resistance which is closely determined by the breakdown voltage of the device

(b) The specific drift resistance is governed by the doping and the thickness of the drift region. Because the critical electric field is 10x higher in SiC than in Si, the doping concentration in the drift region and the thickness of the drift region of a SiC Power MOSFETs can be up to 100x higher and respectively 10x smaller than that in Silicon. Taking into account that the mobility of carriers in Silicon is about 2x of that of carriers in SiC, the specific drift resistance can be ~500X smaller in Sic when compared to Si. This is a very significant advantage, especially for higher classes of voltage ratings (e.g. above 600 V), where the drift region resistance is the most important component of the total on-state resistance.

The JFET resistance is also smaller in SiC, as the extension of adjacent depletion regions associated with the p-well/n-drift region junction is smaller. This is because of the higher doping of the n- drift region in SiC when compared to Si..

The channel and accumulation specific resistances are however higher in SiC than in Si because of the low channel mobility in SiC (30-100x smaller than in Silicon). The channel and accumulation layer resistances tend to be important at lower voltage ratings (e.g. below 600 V), where SiC power MOSFETs have less or no advantages compared to Si Power MOSFETs.

The other resistances play a minor role at higher voltages (e.g. above 600V) where SiC is considered as substitute to Silicon.

(c) (i)

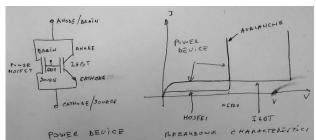

The devices are connected in parallel. Since the MOSFET has a lower voltage rating, the breakdown (which is ~ the rated voltage + a 10% margin) will be dictated by the MOSFET. The MOSFET device will be first to enter the avalanche regime. In other words the power device, combining the two devices will be limited

by the breakdown of the MOSFET (see picture). In terms of the leakage, given that the two devices have the same surface area, the IGBT leakage will be significantly larger than the MOSFET leakage. This is because the leakage is amplified by the bipolar action of the pnp transistor that exists in the IGBT. Therefore the device will have mostly the leakage of the IGBT and the avalanche breakdown of the MOSFET [20%]

(ii) During the reverse conducting mode, only the MOSFET will conduct through its intrinsic PIN diode (also known as the anti-parallel diode). The internal PIN diode in the MOSFET is formed between the p well ( as the anode of the PIN diode), the n- drift region (as the intrinsic region of the PIN diode) and the n+ drain (as the cathode of the PIN diode). No reverse conduction can occur in through the IGBT, as the open-base PNP transistor will block the current during the reverse mode operation. Note that there is no anti-parallel diode present in the IGBT [20%]

Q4. (a) (i)  $V_2 = \frac{M}{M} \frac{D}{C(-D)} V_1$ When smitched on,  $V_1 = \frac{2is}{DT} Lm$ ,  $sisL_m = V_1DT$  $\Delta \phi \cdot N_1 = \sigma i_S L_{IM} = V_1 D T$  $\frac{V_i \partial T}{V_i} = \frac{V_i (1-D)T}{V_i}, \qquad \frac{V_i}{V_i} = \frac{V_i}{V_i} \frac{D}{C_i - o_i}$ Continous flux: NIV, DT = No Vo (1-D)T  $\frac{\sqrt{2}}{\sqrt{1-\sqrt{1-D}}} = \frac{\sqrt{2}}{\sqrt{1-D}} = \frac{\sqrt{2}}{\sqrt{2}}$ the minimum Lm is when critical conduction of flux in the transformer core, i.e. no offset of twx. Due to Cossless system.  $T_i V_i = T_2 V_i$ ,  $T_i = \frac{40 \times 10}{400} = 1A$ When critical conduction of the to ight ament is also in critical condentions. Therefore, for DT, the everye input unsuf I, is hat of the peak current in DT, Irpk = 4 A

$$\frac{Lr}{M} \frac{Cr}{Rr} = \frac{Rr}{M} \frac{8R}{Rr}$$

$$\frac{1}{Rr} \frac{Rr}{Rr} \frac{1}{Rr} \frac{V_{1}}{Rr}$$

$$\frac{1}{Rr} \frac{Lr}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{Lr}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{Lr}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$\frac{1}{Rr} \frac{1}{Rr} \frac{1}{Rr}$$

$$|R_{T}| = |R_{T}|$$

$$|R_{T}| + |R_{T}|$$

$$|R_{$$