#### 4B21 - Analogue Integrated Circuits - SOLUTIONS

#### Question 1

- (a) Feeding back a portion of the output signal and combining it with the external input signal can be used to modify the characteristics of a circuit.

- **(b)** The two kinds of feedback are Negative Feedback used in amplifiers and control systems to improve performance and Positive Feedback used to create oscillators.

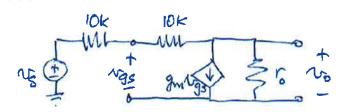

(c) (i)

Type of feedback arrangment: shunt-shunt (sampled signal = voltage, feedback signal = current)

(c) (ii)

(c) (iii)

$$\beta = -\frac{1}{10k} = -10^{-4} \text{ A/V}$$

(c) (iv)

$T_{0} = K (V_{6S} - V_{4})^{2} \text{ where } k = \frac{1}{2}h C_{0X} \frac{h_{0}}{L}$ Assume  $0 \le V_{4} \le 2V$  and  $0 < K \le 0.2 \text{ mA/V}^{2}$ Carry values that fall in this varge are acceptable)

We choose  $V_{4} = 2V$  and  $K = 0.125 \text{ mA/V}^{2}$   $(mA = 0.125 \times 10^{3} \frac{mA}{V^{2}} (V_{6S} - V_{4})^{2} \Rightarrow (V_{6S} - V_{4})^{2} = 8$ So  $(V_{6S} - V_{4}) = \pm V_{8} = \pm 2.83V$ Hence  $V_{CS} = 4.83V$  (since the other solution of -0.83V does not turn on transistor)

Gain of transversitance amplifies is  $A = -gm(10K/110K)(V_{6}/110K)$ Cosming  $V_{6S} > 10K$ ,  $V_{6S} = -gm(5K/10K)$   $V_{6S} = (V_{6S} - V_{4}) = 2\times 0.125 \times 2.83 = 0.71 \text{ mA}$ So  $V_{6S} = -0.71 \text{ mA} \times 5\times 10^{7} \text{ y/A} = -3.5\times 10^{4}$   $V_{6S} = (V_{6S} - V_{4}) = -3.5\times 10^{4} + (V_{6S} - V_{4}) = -3.5\times 10^{4} + (V_{6S} - V_{6S}) = -3.5\times 10^{4} + (V_{6S}$

(c) (v)

#### Benefits:

- Increase in bandwidth

- Decrease in non-linear distortion

- Control over input and output impedances

- Desensitization of gain

- Decrease in noise

## Drawback:

- Decrease in gain

#### Question 2

(a) Although the basic CMOS technology requires additional processing steps compared to the NMOS technology, it provides devices with complementary symmetry, i.e. p-channel transistors can be used as active loads in conjunction with n-channel transistors to obtain high voltage gain and DC level shifting.

(b)

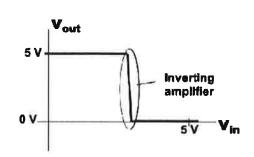

The static operation of a generic CMOS inverter circuit is characterized by its voltage transfer characteristic. Here, if the input is HIGH (e.g.,  $v_{\rm in} \sim 5$  V), the output is low ( $v_{\rm out} \sim 0$  V), and vice-versa. The logic inverter circuit is basically an inverting amplifier that is utilized in the extreme regions of operation whereby the transistors are in switch (on or off) mode. In the intermediate (or transition) region, however, such as at the output HIGH-to-LOW or LOW-to-HIGH transition, the inverter circuit behaves as an inverting linear amplifier with characteristic,  $v_{\rm out} = -Av_{\rm in}$ . Here, A is the circuit gain.

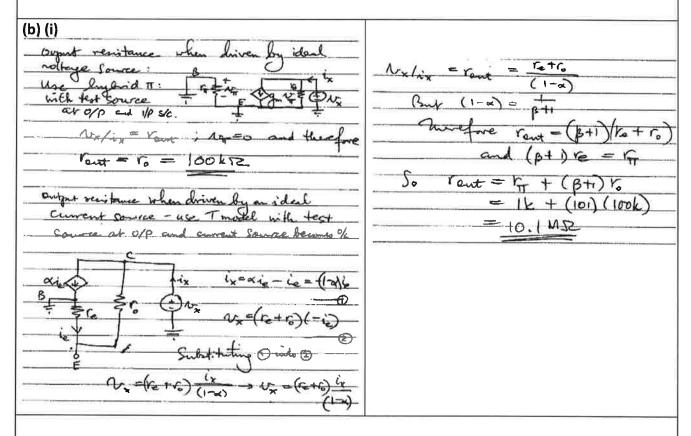

(c) (i)

For  $Q_2$  to be saturated, we need  $V_{DS} \in V_{GS} - V_{\xi}$ where  $V_{GS}$  and  $V_{\xi}$  are regative. But  $V_{DS} = V_{GS}$   $\Rightarrow V_{GS} \in V_{GS} - (-2) = 0 \ ( \le +2, so \ Q_2 \text{ saturated})$ Since  $Q_2$  is saturated,  $I_D = K(V_{GS} - V_{\xi})^2$   $V_{GS} = V_{DS} - \pm \sqrt{\frac{1}{10}} + V_{\xi} = \pm 5 - 2$   $= \int_{S} 3V$ For  $Q_2$  to be on ,  $V_{GS} = V_{\xi}$ , so  $V_{GS} = -7V$ So  $V_{SG} = V_{SD} = 7V$ , hence  $V_D = 10 - 7 = 3V$  (c) (ii)

Equivalent wint for  $Q_2$  in this information is

as much theme

as muc

(c) (iii)

$\begin{array}{lll}

& V_{A}/I_{D} = 40 \, k\Omega \\

& \sqrt{100} = 2 \, k(V_{6S} - V_{1}) = 0.2 \, x_{10} \, \lambda_{10} \, \lambda_{10} \, \lambda_{10} \\

& = 1 \, m_{A}/V \\

& = 1 \, m_{A}/V \\

& = 2 \, k(|V_{6S}| - |V_{1}|) = 2 \, x_{10} \, \lambda_{10} \, \lambda_{10$

(c) (iv)

by inspection, Rin-Rillez = Kikz

= 4.8M52 Rikz

Rout is obtained when Nin= Ngs = 0

Ro = Vollyn 2 fm

= 40×1 kiz = 0.98 kiz

40+1

Vaut 2 - gm Ngs (fm) 2-Ngs

= -10<sup>3</sup> × Nm × 10

Vaut/Nm = -1.

### **Question 3**

(a) Ideal voltage source is one where the voltage across it is independent of the current through it. Ideal current source is one where the current through it is independent of the voltage across it.

(b) (ii) The common-base amplifier, when driven by low source resistance, behaves as a voltage amplifier. On the other hand, with high source resistance, it behaves like a current follower. This transition takes place when the source resistance is at the vicinity of the emitter resistance,  $r_{e^+}$

### **Question 4**

- (a) A multistage amplifier is formed by combining several several stages connected in a cascade as in output of the first stage connected to form input of second stage and so on to achieve the performance as required in many applications, which is otherwise not attainable with a single stage amplifier.

- (b) If the gain of each amplifier stage is expressed in dB, then the total gain is the *sum* of the gains of the individual stages: Gain in dB (A) =  $A_1 + A_2 + A_3 + A_4 + ... A_n$

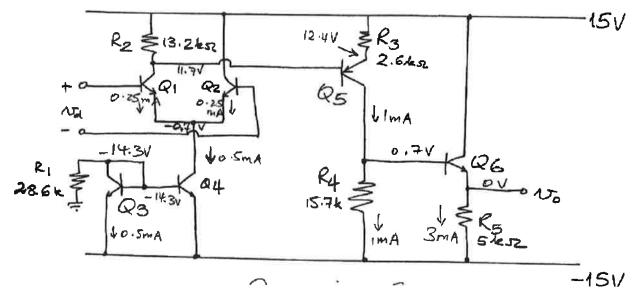

- (c) (i) Functionality of each transistor: Q3,4 current source for biasing input stage, Q1,2 input stage with differential in and single-ended out (i.e. differential to single-ended conversion), Q5 DC level shifting, Q6 emitter follower output stage.

- (c) (ii) The DC voltages and currents are as indicated on circuit shown assumptions used:  $V_{BE} = 0.7V$  and negligible base currents.

(c) (iii)

(epper limit is set by Q1 and Q2

VB = VC = 11.7V

Power limit is set by Q4; VCQ4

So VB1 = VB2 = -14.3V + 0.7V = -13.6V

13.6V ≤ common mode range ≤ 11.7V

# (c) (iv) Input and Output Resistance

Oupput Resistance, Rout

# Gain of the various stages

$$Ve_1 = Ve_2 = \frac{25mV}{0.25mk} = \frac{10052}{20052} = \frac{-62.9 \text{ V/V}}{20052}$$

## gain due to Q5

$$R_{\text{out}} = R_5 / \left[ \frac{R_4}{101} + r_{\text{e.s.}} \right] = 5000 / / (63.8)$$

$$= 158.652$$

The of the various stages

$$G_{\text{out}} = \frac{R_5}{R_5} = \frac{5000}{5000 + \frac{25}{3}}$$

$$= 0.938 \text{ V/V}$$