# EGT3 ENGINEERING TRIPOS PART IIB

Tuesday 22 April 2014 2 to 3.30

### Module 4B21

## ANALOGUE INTEGRATED CIRCUITS

Answer not more than three questions.

All questions carry the same number of marks.

The *approximate* percentage of marks allocated to each part of a question is indicated in the right margin.

Write your candidate number <u>not</u> your name on the cover sheet.

## STATIONERY REQUIREMENTS

Single-sided script paper

## SPECIAL REQUIREMENTS TO BE SUPPLIED FOR THIS EXAM

CUED approved calculator allowed Engineering Data Book Attachments: Values of constants and relevant formulae (1 page)

## You may not start to read the questions printed on the subsequent pages of this question paper until instructed to do so.

(d)

1 (a) What is feedback as applied to an electrical circuit? [10%]

(b) Name the two kinds of feedback arrangement used in electrical circuits along with one example of each. [10%]

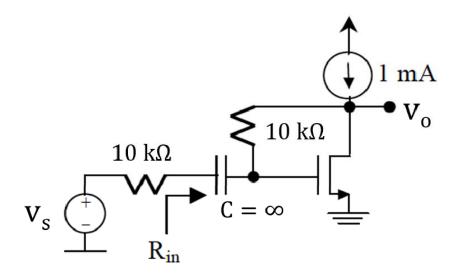

(c) For the amplifier circuit and transistor parameter values given in Fig. 1, assuming mid-band frequency operation,

Figure 1

| (i)           | Define the type of feedback arrangement.                                                                                      | [109 | %] |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|------|----|

| (ii)          | Construct and label the small-signal equivalent circuit.                                                                      | [209 | %] |

| (iii)         | What is the value of the feedback network gain, $\beta$ ?                                                                     | [159 | %] |

| (iv)<br>overa | Using feedback techniques along with reasonable approximations, find the all voltage $v_o/v_{s.}$ State any assumptions made. | [204 | %] |

| List f        | Five benefits and one drawback of the above feedback arrangement.                                                             | [159 | %] |

2 (a) Why does the CMOS technology offer higher design flexibility for analogue functions compared to the NMOS technology? [20%]

(b) Describe the static operation of a generic CMOS inverter circuit aided by a sketch of its voltage transfer characteristic. [20%]

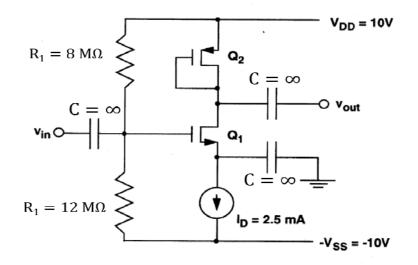

(c) For the CMOS amplifier shown in Figure 2 with the indicated values of components,

(i) Determine the DC value of the drain voltage  $V_D$ . [15%]

(ii) Show that the PMOS transistor  $Q_2$  can be replaced by an ac equivalent resistance of approximately  $l/g_m$ . [15%]

(iii) Calculate the ac parameters and construct the small-signal equivalent circuit of the amplifier. [15%]

(iv) Calculate the amplifier's input resistance  $(R_{in})$ , output resistance  $(R_{out})$  and the voltage gain  $(v_{out}/v_{in})$  for mid-band frequency operation. [15%]

In your calculations, you can assume that  $|V_t| = 2 V$ ,  $|V_A| = 100 V$ , and  $K = 0.1 mA/V^2$  for both transistors.

Figure 2

Page 3 of 6

(TURN OVER

3 (a) Explain what is meant by an ideal voltage source and an ideal current [30%]

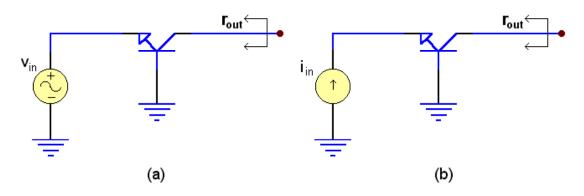

(b) Shown in Figure 3 are two common-base (CB) amplifiers, driven by (a) an ideal voltage source and (b) an ideal current source, respectively.

(i) Assuming that each circuit has been properly biased, and that the biasing networks, although not indicated in Fig. 3, do not affect the small-signal analysis, calculate the output resistance,  $r_{out}$  for circuits (a) and (b), using the following data:  $r_{\pi} = 1 \ k\Omega$ ,  $r_o = 100 \ k\Omega$ , and  $\beta = 100$ .

(ii) Comment on the physical implications of the results for  $r_{out}$  for the two configurations. [20%]

Figure 3

[50%]

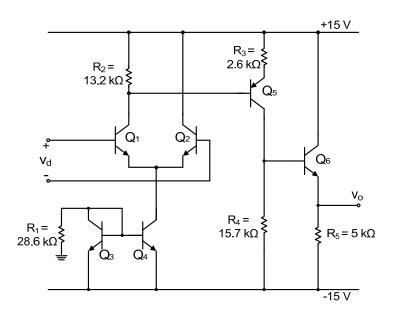

4 Why are multi-stage amplifiers necessary from the standpoint of achieving (a) the desired circuit characteristics? [15%] State the expression for the overall gain of a multistage amplifier of n stages, in (b) decibels, expressed in terms of the gain of the individual stages. [10%] In the multi-stage amplifier circuit shown in Fig. 4, (c) (i) State the functionality of each transistor. [20%] (ii) Calculate the necessary DC voltages and currents. Clearly state all assumptions. [20%] (iii) What is the common-mode voltage range? [15%]

(iv) Find the input resistance, output resistance, and voltage gain  $(v_o/v_d)$ . [20%]

Assume that all transistors are matched with  $\beta = 100$  and  $V_{BE} = 0.7$  V

### **END OF PAPER**

THIS PAGE IS BLANK

# Version AN/3 FORMULA SHEET

**Bipolar Junction Transistors:**

$i_{C} = \alpha i_{E} \qquad i_{C} = \beta i_{B} \qquad i_{B} = (1-\alpha)i_{E} \qquad i_{E} = (\beta+1)i_{B}$   $\beta = \frac{\alpha}{1-\alpha} \qquad \alpha = \frac{\beta}{\beta+1} \qquad V_{T} = \frac{kT}{q} = 25 \ mV \ at \ 300K$   $g_{m} = \frac{I_{C}}{V_{T}} \qquad r_{\pi} = \frac{V_{T}}{I_{B}} \qquad r_{e} = \frac{V_{T}}{I_{E}} \qquad r_{o} = \frac{V_{A}}{I_{C}}$

MOSFETs:

$$i_{D} = K[2(v_{GS} - V_{t})v_{DS} - v_{DS}^{2}]; \qquad i_{D} = K(v_{GS} - V_{t})^{2} = \frac{k'}{2} \left(\frac{W}{L}\right) (v_{GS} - V_{t})^{2}$$

$$K = \frac{1}{2} \mu C_{ox} \left(\frac{W}{L}\right) \qquad k' = \mu C_{ox} \qquad g_{m} = 2K (v_{GS} - V_{t}) \qquad r_{o} = \frac{|V_{A}|}{I_{D}}$$

Differential Amplifiers:

$$v_{o} = A_{d}v_{d} + A_{cm}v_{cm}; \qquad CMRR = 20 \log|A_{d} / A_{cm}|$$

$$A_{cm} = \frac{v_{o}}{v_{cm}} \text{ or } A_{cm} = \frac{\Delta R_{D}}{2R}; \qquad A_{d} = \frac{v_{o}}{v_{d}} = g_{m}R_{D} \text{ or } A_{d} = \frac{\Sigma R_{C}}{\Sigma R_{E}}$$

BJT small-signal operation:

$$i_{C1} \approx \frac{\alpha I}{2} + \frac{\alpha I}{2V_T} \frac{v_d}{2}$$

$i_{C2} \approx \frac{\alpha I}{2} - \frac{\alpha I}{2V_T} \frac{v_d}{2}$

$$\begin{aligned} R_{id} &= 2(\beta + 1)(r_e + R_E) & R_E = emitter \ resistance \\ i_{D1} &\approx \frac{I}{2} + \left(\frac{I}{V_{GS} - V_t}\right) \frac{v_{id}}{2} & i_{D2} \approx \frac{I}{2} - \left(\frac{I}{V_{GS} - V_t}\right) \frac{v_{id}}{2} \\ C_{eq} &= C_{bridge} (1 - K) & K \equiv \frac{V_2}{V_1} \end{aligned}$$

FET small-signal operation:

Millers Theorem: