### ENGINEERING TRIPOS PART IA

Monday 11 June 2007

9 to 12

Paper 3

# ELECTRICAL AND INFORMATION ENGINEERING

Answer all questions.

The approximate number of marks allocated to each part of a question is indicated in the right margin.

Answers to questions in each section should be tied together and handed in separately.

There is one attachment.

STATIONERY REQUIREMENTS

SPECIAL REQUIREMENTS Single-sided script paper **Engineering Data Book** CUED approved calculator allowed

> You may not start to read the questions printed on the subsequent pages of this question paper until instructed that you may do so by the Invigilator

## SECTION A

1 (long) (a) Explain briefly how the techniques of mesh current analysis and loop current analysis are used in d.c. and a.c electrical circuits.

[5]

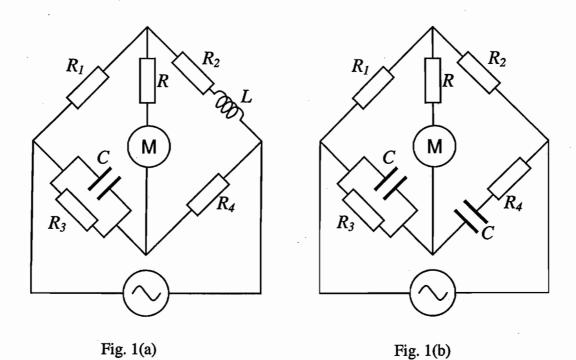

(b) Figure 1(a) shows the circuit for an a.c. bridge. The voltage source supplies a sinusoidal waveform of frequency  $\omega$ . At balance the current through the meter M is zero. Find the condition for balance in terms of  $R_I$ ,  $R_2$ ,  $R_3$ ,  $R_4$  and the ratio L/C.

[17]

[8]

(c) Consider the bridge in Fig. 1(b). Find an expression for the frequency  $\omega$  at which the bridge balances, in terms of  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$  and C.

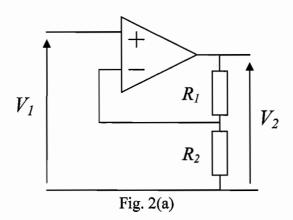

- 2 (long) (a) Explain what is meant by an ideal operational amplifier, with particular reference to gain, input resistance and output resistance. Explain how the ideal op-amp approximations may be used to simplify the analysis of op-amp circuits.

- [5]

- (b) The op-amp in Fig. 2(a) may be assumed as ideal, except for the finite gain A. Derive an expression for the voltage gain  $V_2/V_1$  in terms of  $R_1$  and  $R_2$ . [5]

- (c) Calculate  $V_2/V_1$  if  $R_1=150k\Omega$ ,  $R_2=2k\Omega$  and  $A=10^5$ . [5]

- (d) If instead the op-amp has a finite output resistance  $R0=150\Omega$ , show that Rout $\approx R0(R1+R2)/(AR2)$  and calculate Rout. [10]

- (e) The load capacitor in Fig. 2(b) is connected to the circuit of case (d). Calculate C so that  $V_C$  drops 3dB from its mid band value at 10 kHz. [5]

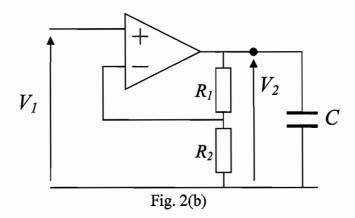

- 3 (short) (a) Define  $r_d$  and  $g_m$  in the small-signal a.c. model of a JFET. [3]

- (b) Consider the circuit in Fig. 3. Find values for  $R_I$  and  $R_2$  required to set the transistor d.c. operating point to  $V_{DS} = 14$  V,  $I_D = 0.3$  mA and  $V_{GS} = -3$ V. Assume an ideal transistor and zero gate current. [3]

- (c) Draw the small-signal circuit valid for mid-band frequencies, and find the mid-band small-signal gain,  $V_o/V_i$ . For the JFET small-signal parameters take  $r_d = 30 \text{ k}\Omega$  and  $g_m = 5 \text{ mS}$ . [4]

- 4 (short) A small factory consumes 30 kW with a lagging power factor of 0.7 at the factory. When it is connected to a 50 Hz supply the voltage across the factory terminals is 240 V. The supply line has an impedance  $Z_s = 0.02 + j0.04 \Omega$ .

- (a) Draw the circuit diagram and calculate the real power lost in the line and the voltage supplied at the input. [5]

- (b) Assuming that the voltage across the factory terminals continues to be 240 V, calculate the required size of the capacitor connected across the factory terminals in order to correct the power factor to unity. [5]

5 (short) A non-ideal transformer is short-circuit tested and open-circuit tested to measure its characteristics. The open-circuit test gives  $V_{primary} = 240 \text{ V}$ ,  $I_{primary} = 0.2 \text{ A}$ , P = 15 W,  $V_{secondary} = 120 \text{ V}$ . The short-circuit test gives  $V_{primary} = 40 \text{ V}$ ,  $I_{primary} = 3 \text{ A}$ , P = 30 W. Determine the values of the equivalent circuit parameters referred to the primary side of the transformer. (See page 20 of the Electrical and Information Data Book for the non-ideal transformer equivalent circuit) [10]

#### **SECTION B**

- 6 (long) (a) A lift between two floors has inside Up (U) and Down (D) buttons. Press U while on the bottom floor and the doors will begin to close but will reopen if D is pressed before a sensor (S) senses that the doors are shut. Once the doors are shut, the lift moves to the top floor then opens its doors. The same procedure happens on the top floor but with the direction of the lift and roles of U and D reversed. A clock latches the button and door sensor inputs every half a second and the doors take 3 seconds to close. Draw a state diagram for this system.

- (b) The lift is to be controlled by a set of J-K bistables. Explain how many bistables are needed and draw the state table. [10]

- (c) Draw a complete circuit diagram. [10]

[10]

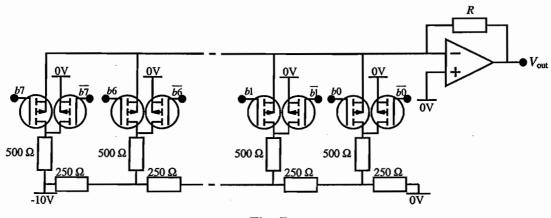

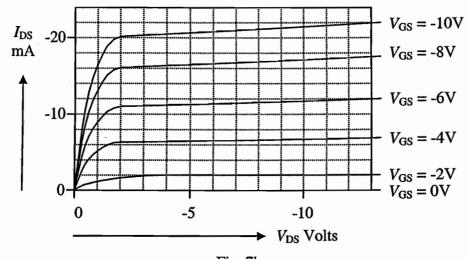

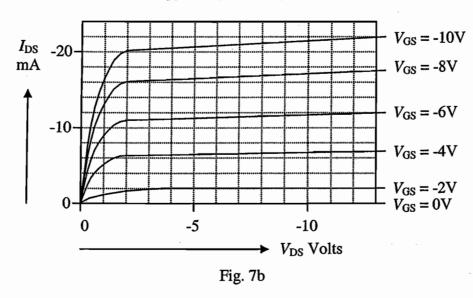

- 7 (long) Figure 7a shows an 8 bit digital-to-analogue converter and Fig. 7b shows the characteristics of all the transistors used in the circuit.

- (a) By drawing a load-line or otherwise, find the drain source voltage across the far left transistor when its gate voltage b7 is -10 V and the gate voltage  $\overline{b7}$  is 0 V. A duplicate of Fig. 7b is provided at the end of this paper and you should hand it in with your answer. [10]

- (b) What value should R be if the output is to be 5 V when the gates b7 and  $\overline{b6}$  to  $\overline{b0}$  are at -10 V and the gates of all the others are at 0 V? [10]

- (c) If the tolerance of the 250  $\Omega$  and 500  $\Omega$  resistors is 1%, what is the maximum error in the output when the gate voltages are as in (b)? What factor of the correct output will this error be when only the least significant bit is set? [10]

Fig. 7a

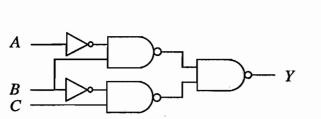

8 (short) Show that the Boolean expression:

$$A.B + C.D = (A + C).(B + D)$$

is true if two of the variables are the inverse of one another, and state which are these variables.

[10]

9 (short)

| Fig  | Q   |

|------|-----|

| 1.15 | . フ |

|     |   | BC |    |    |    |  |

|-----|---|----|----|----|----|--|

|     |   | 00 | 01 | 11 | 10 |  |

| A · | 0 | 0  | 1  | 1  | 1  |  |

|     | 1 | 0  | 1  | 0  | 0  |  |

- (a) Explain the circumstances under which the truth table of Fig. 9 may not accurately describe the behaviour of the circuit. [7]

- (b) How would you modify the circuit so that the truth table is accurate? [3]

#### SECTION C

10 (short) A metal sphere of radius 10 mm is placed with its centre 50 mm above an infinite conducting plane and the sphere is then charged to 50 V. What is the approximate electric field at the conducting plane under the centre of the sphere?

[10]

11 (short) A straight infinitely long wire is placed in the plane of a square coil and parallel to one side as shown in Fig. 11. Each side of the coil is of length 5 mm. What is the flux through the coil if its centre is 100 mm from the wire which carries a current of 1 A? If the current in the wire alternates at 50 Hz, approximately how many turns should the coil have to generate an alternating potential of  $1 \,\mu\text{V}$  across its terminals?

[10]

Fig. 11

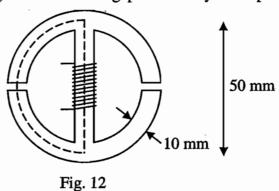

12 (short) A 2 mm thick iron plate has a relative permeability of 1000. It is cut into a bar within an annulus, both of which are 10 mm wide as shown in Fig. 12. The annulus has an average diameter of 50 mm. If 0.5 A is passed through a coil of 300 turns round the bar and 2 mm gaps are cut between the top and bottom halves of the annulus either side of the coil, what is the magnetic field in the gaps? State any assumptions made.

[10]

**END OF PAPER**

# Candidate number:

# Copy of Fig. 7b for question 7

Detach this sheet and hand it in with your answers for section B.