# STATIC-1 HAZARD IS L'HOW A SIGNAR

GIVER BY (J+J) SHOULD BU HIGH FOR BOTH CONDITIONS OF X- AND YET IS LOVE BRIEFLY DE PO THE WIRE BER DERAY FORTING +

A FUNCTIONAR HADAGO IS CAUSED BY CHANGES OF 2 OR TORE IMPUT LARIABLES AT ATIME-

A DYDANIC HATARD IS RAPRE A SILVER ON PUT MANGE 15 88000000 Dro YER JU 03 ZVZ 15 FOUND. PORE 74AN ONE IMPOR CONDUCTE AT A

7100

AN ESSERTIAT HATARD IS CAUSED BY A RACE BETWEEN AN INPUT SIGNAZ CHARTOS AND AZI OSTRITCHANOS

(b) A POS EXPESSION WILL DOT CONTAIN STATIC AND DYNAMIC HARARDS IF!

1. ALL ABJACENT O" SQUARES IN THE K- MAR OF THE COMPLETIENT OF THE SULTERING FUNCTION ARB CONTINUES BY A CONTINUE OF PERO 7. THERE ARE NO O- TERROS TODAT CONTAIN BOTA A VARIABLE ADD ITS CONPLETIONS

1) HAND: GOT IF BY MAPPING "1"S in PHO K-MP. MAKE SURE THAT AZI ANACOUNT 15 ARF GUERAD BY A CONTON LOSP F= CA + ABD + BBC T= CA + BD (A+C) = CA. BD/A+C) CÁ. BD. ĀC

1100) (11 NAR FERES FOR FOR T=DA + EB + AE + BE F= A (B+D) + E (D+ A+B) = A + B+D

1) AB F = A.B + A.B. + A.E.S. (OR BED) T = A.B - (ACD) = (A+B) - (A+B+C) . (A+C+D) J(A)) A MUSTIPLOS OR WITH GATROL LINDS , YIERDS AN OUTPUT Do PF + D, PP + D, P9+B, PP SELECTISG THE FOIR DATA LIVES in TURN AS PG CARAGO Do, D1, D2, D3 WE NOTE THAT A, B ARG USOD IN ALL THE TERROS IN the DESIRED FUNCTION

Y= A.B. + ABE+ABC  $P \neq A = P \qquad B = 9$ 1 PQ + CPQ+ CPQ CoopArena D= 1 DIEC Dz= 0 D3 = C GATROL LINE SELECTION BEPASO 南 作 D=1,0=9 0200 (NEUTS D, CDZ StAPPED SO D35 C)

.

IN THE POORE SEPONTIAL NETWORK THE MUTARY DUT RUTS, Z ARE A FUNCTION THE PRESENT STATES OLLY Z= f(4) WHEREAS IN THE POBACY SEQUENTIAR NATUORN THE ARITARY DUT RUTS AND A FUNCTION BUTA THE PRESENT STATES AND VHE PRIMARY WRUTS 7- f(t,9). THE CHOICE OF THE DETWORK IS ONE OF CONVENIENCE AND PERSONAL AURENOSCO, OUT MEAN PODER IS MONE GENERAL THE POST SION FROM OFERA TIONAR DIFFORMERO BETHEREN THE TREO IS THAT CHESS A SET OF INPOSS IS APPLIED TO VAS POORE NETWORK, THE RESULTION ON PORT DO LOT ARREAD DATE APPEAR RUSH CAUSES THAT FLIP-FLOPS THE CLOCK NO CAMPOR STATE

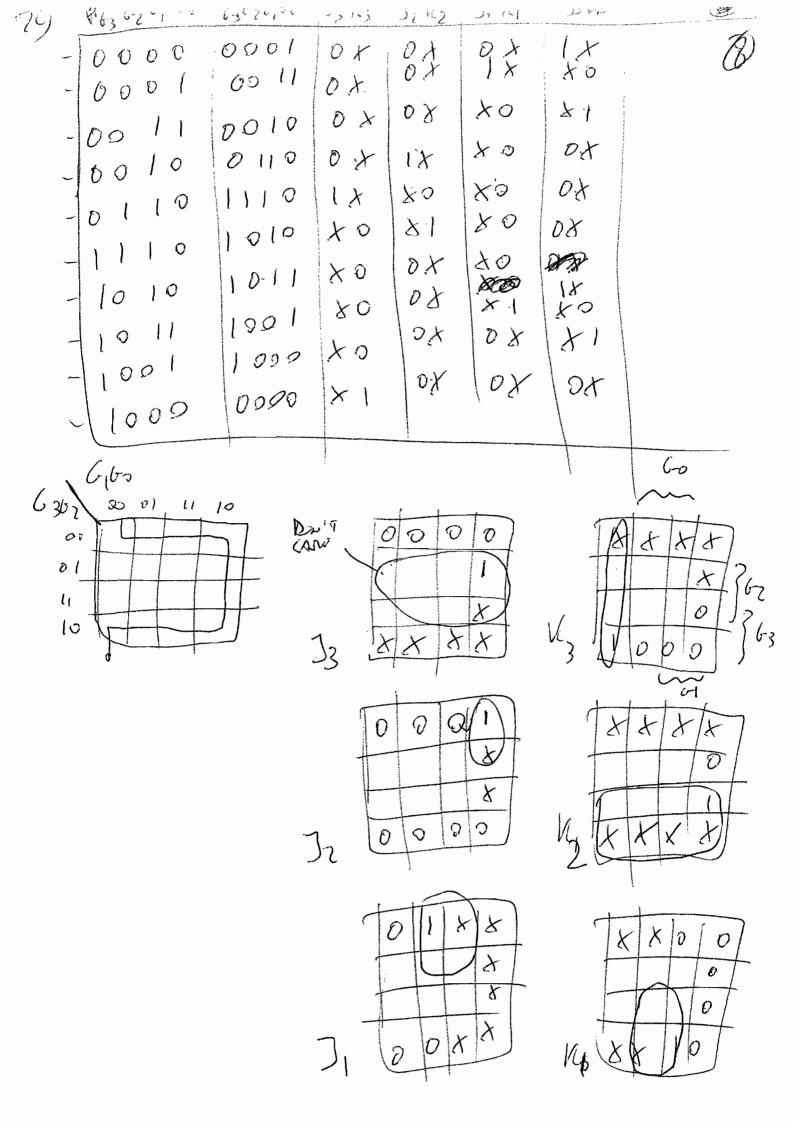

4)

$$\begin{cases}

J_{3} = 6_{2} \\

K_{3} = 6_{3} & 6_{1} & 6_{0}

\end{cases}$$

$$\begin{cases}

J_{1} = 6_{3} & 6_{1} & 6_{0}

\end{cases}$$

$$\begin{cases}

J_{1} = 6_{3} & 6_{0}

\end{cases}$$

$$\begin{cases}

V_{1} = 6_{3} & 6_{0}

\end{cases}$$

$$\begin{cases}

V_{1} = 6_{3} & 6_{0}

\end{cases}$$

$$\begin{cases}

V_{2} = 6_{3} & 6_{1} + 6_{3} & 6_{1}

\end{cases}$$

$$\begin{cases}

V_{2} = 6_{3} & 6_{1} + 6_{3} & 6_{1}

\end{cases}$$

Ory To AND 16 HAVE OR

# Part IIA Paper 3B2

**Solutions**

## On A

(a) Historically logic circuit development began with bipolar devices operating between saturation and cut-off. Available process technologies encouraged this development in an evolutionary rather than revolutionary way. For saturating bipolar technology:

# Advantages:

- superiority over passive (e.g. diode-based) logics

- technological simplicity

- adequately suited to integration

- some scope for enhancement (e.g. use of schottky diode technology)

## Disadvantages:

- high device count per function

- high power consumption

- low input resistance

- long propagation times

- limited enhancement potential via scaling

The main problem that had to be surmounted was the undesirable switching delay as devices came out of saturation. This was partly resolved by use of Schottky transistors. Nonetheless, TTL, S/LS TTL, ALS TTL were the primary technology on which much of the emergence of digital computing depended. Fastest logics ran at c. 100 MHz and required a fixed 5V supply. The limited switching speed was circumvented with the introduction of current-mode or non-saturating logic e.g. ECL.

## Advantages

- very high speed, to > 1GHz in recent forms

- constant power consumption (approx) leading to:

- good overall noise characteristics

#### **Disadvantages**

- very high consumption

- poorly suited to large-scale integration

The introduction of ion implantation facilitated the full development of complementary MOS technology, allowing accurate positioning of n dopants in p substrates and v.v. For CMOS:

# **Advantages**

- very low consumption for LF applications

- very good noise immunity (up to 0.4 VDD for inverter)

- fully restored logic outputs, 0V and VDD

- operable over range of supply voltages

- gate inputs draw no current, easy to drive

- highly suited to integration

- scales well (consumption & speed improve as devices shrink)

- usable up to about 60GHz

# **Disadvantages**

- · comparatively poor drive capability

- not as fast as best bipolar forms for significant loads

- sensitivity to static breakdown

- consumption increases with operating frequency > 1GHz

- liability to destructive latch-up (poor design or peripheral failures)

With CMOS the dominant mode of energy loss is dynamic dissipation as nodal capacitances are charged/discharged. Straightforward approaches to logic involve multiple devices and significant nodal capacitances, so much effort has gone into circuit abstraction. The excellent drive capability of bipolar is put to good use in BiCMOS which has superior performance when driving significant loads. The recent emergence of Ge-doped Si semiconductors is leading towards still greater speed improvements up to about 100 GHz is promised by this approach. The use of III/V semiconductors, e.g. GaAs in MESFETS has offered propagation delays o(1 ps) but so far large scale integration has not been practicable.

# Part IIA Paper 3B2

Solutions

(b) As all devices are operating in non-saturation, we can write for  $I_2$  in  $T_2$ :

$$I_{2} = \frac{k'}{2} \frac{W}{L_{2}} \left[ 2(V_{GS2} - V_{T})V_{DS2} - V_{DS2}^{2} \right]$$

Hence  $I_{2} \frac{2L_{2}}{k'W} = \left[ 2(V_{GS2} - V_{T})V_{DS2} - V_{DS2}^{2} \right]$

(1)

Similarly for I1 in T1

$$I_{1} \frac{2L1}{k'W} = \left[ 2(V_{GS} - V_{T})V_{D1S} - V_{D1S}^{2} \right]$$

(2)

$V_{GS2} = V_{GS} - V_{D1S}$  and  $V_{DS2} = V_{DS} - V_{D1S}$ ; substitute (2) into (1) Note that:  $I_2 \frac{2L_2}{k'W} = \left[ 2(V_{GS} - V_{D1S} - V_T)(V_{DS} - V_{D1S}) - (V_{DS} - V_{D1S})^2 \right]$  $= \left[2(V_{GS}-V_T)V_{DS}-2(V_{GS}-V_T)V_{D1S}-2V_{D1S}V_{DS}+2V_{D1S}^2+V_{DS}^2+2V_{DS}V_{D1S}+V_{D1S}^2\right]$  $= [(2(V_{GS} - V_T)V_{DS} + V_{DS}^2) - (2(V_{GS} - V_T)V_{DIS} - V_{DIS}^2)]$

By inspection, the second term inside the [] square brackets is equivalent to the RHS of (2). So substituting:

$$I_2 \frac{2L_2}{k'W} = \left[ 2(V_{GS} - V_T)V_{DS} + V_{DS}^2 \right] - I_1 \frac{2L_1}{k'W}$$

But by Kirchhoff  $I_2 = I_1 = I$ , say. Hence,

$$\frac{2I(L_1 + L_2)}{k'W} = \left[2(V_{GS} - V_T)V_{DS} + V_{DS}^2\right], \text{ which gives}$$

$$I = \frac{k'}{2} \frac{W}{L_1 + L_2} \left[2(V_{GS} - V_T)V_{DS} + V_{DS}^2\right]$$

By inspection, this is the current that would flow in a single device T of width W and length  $L_2 + L_1$ , and whose electrode voltages are  $V_{GS}$ ,  $V_{DS}$  as shown.

(c) From above, the equivalent circuit is:

For the n-type, (from above)

$$k_n = \frac{k'_n W}{L} = \frac{8 \times 10}{2} = 40 \,\mu\text{A/V}^2$$

For the n-type, (from above)  $k_n = \frac{k'_n W}{L} = \frac{8 \times 10}{2} = 40 \,\mu\text{A/V}^2$   $V_{GS} = 1.5 \text{V}$   $\frac{8}{1}$  For the p-type,  $k_p = \frac{k'_p W}{L} = \frac{(4+4) \times 5}{1} = 40 \,\mu\text{A/V}^2$

For the p-type,

$$k_p = \frac{k'_p W}{L} = \frac{(4+4) \times 5}{1} = 40 \text{ } \mu\text{A/V}$$

Hence, by symmetry,  $V_{\text{out}} = V_{\text{DS}} = V_{\text{DD}}/2 = 1.5 \text{ V}$ , and for each transistor,  $V_{DS} > V_{GS} - V_{T}$

And

$$I_D = \frac{k}{2} (V_{GS} - V_T)^2 = 40(1.5 - 0.5) = 40 \,\mu\text{A}$$

# Qn B

(a) In ECL the transistors are configured as a form of differential amplifier in which current is steered between one member of the differential pair (representing logic 0), and the other member (representing logic 1). Thus the net current in the tail remains reasonably constant. Current is controlled by applying inputs symmetrically disposed about a carefully defined point in the active region determined by an accurate reference voltage applied to the base. The reference voltage is generated on-chip using a circuit that is stable and temperature-compensated. The logic output swing of the circuit is also symmetrical about the reference, and it is small enough to ensure that with the loads provided, no transistor enters saturation. Emitter followers are incorporated to protect the sensitive differential pair from external loading effects and to give large fan-out. In this way the objectionable time delays associated with saturating bipolar logic may be avoided, but the constant significant current drain leads to large power consumption.

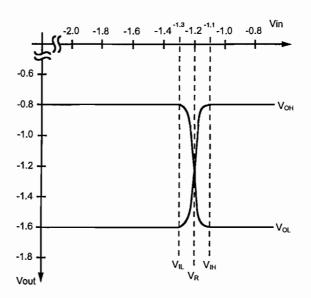

(b) The required logic swing, being  $V_R \pm 0.4$  V, is symmetric as described above. The logic levels are:  $V_{\rm OH} = -1.2 + 0.4 = -0.8$  V, and  $V_{\rm OL} = -1.2 - 0.4 = -1.6$  V. In the calculations that follow, all base currents are ignored, i.e. assumed to be zero. This implies that  $I_C = I_E$  in all devices.

We begin by determining suitable values for  $R_1$  and  $R_2$  such that the two emitter follower transistors provide the correct  $V_{OH}$ . For maximum speed we operate these devices with the highest allowable emitter current  $I_E$  of 5 mA.

$$R_1 = R_2 = \frac{V_{OH} - V_{EE}}{I_E} = \frac{-0.8 + 5.2}{5 \times 10^{-3}} = 0.88 \text{ k}\Omega$$

Next determine the value for  $R_E$  by considering the case where  $T_1$  is on (conducting more than  $T_2$ ), with  $V_{B1} = V_{OH}$ . Again for speed we allow  $I_{E1}$  to be the maximum permitted value of 5 mA. Hence:

$$R_{\rm E} = \frac{V_{OH} - V_{BE1} - V_{EE}}{I_{E1}} = \frac{-0.8 - 0.8 + 5.2}{5 \times 10^{-3}} = 0.72 \text{ k}\Omega$$

$R_{\rm Cl}$  is then calculated assuming that  $V_{\rm Ol}$  produces the correct value of  $V_{\rm OL}$

$$R_{C1} = \frac{V_{CC} - (V_{OL} + V_{BE3})}{I_{E1}} = \frac{0 + 1.6 - 0.8}{5 \times 10^{-3}} = 0.16 \text{ k}\Omega$$

When  $T_2$  is on, its current is set by the reference voltage  $V_R = -1.2$  V applied to its base:

$$I_{E2} = \frac{V_R - V_{BE2} - V_{EE}}{R_E} = \frac{-1.2 - 0.8 + 5.2}{0.72 \times 10^3} = 4.44 \text{ mA}$$

Finally,  $R_{C2}$  is determined knowing  $I_{E2}$ , requiring  $V_{O2}$  to be  $V_{OL}$

$$R_2 = \frac{V_{CC} - (V_{OL} + V_{BE4})}{I_{E2}} = \frac{0 + 1.6 - 0.8}{4.44 \times 10^{-3}} = 0.18 \text{ k}\Omega$$

Solutions

(c) The voltage transfer characteristic is shown below. The transition is centred upon  $V_R$ , and is stated to be of width 200 mV. The output swing is likewise centred on  $V_R$  but has greater amplitude, of  $\pm$  0.4 V which is ample to drive a succeeding ECL stage effectively. Formally, the noise margins may be evaluated, and these can be seen to be 0.3 V for both the high and the low state.

$$V_{\rm OH} = -0.8 \text{ V}$$

$V_{\rm OL} = -1.6 \text{ V}$

$$V_{\rm IH} = -1.1 \text{ V}$$

$V_{\rm IL} = -1.3 \text{ V}$

$$NM_{\rm H} = V_{\rm OH} - V_{\rm IL} = -0.8 + 1.1 = 0.3 \text{ V}$$

$$NM_L = V_{IL} - V_{OL} = -1.3 + 1.6 = 0.3 \text{ V}$$