## ENGINEERING TRIPOS PART IIB

Friday 5 May 2006

9 to 10.30

Module 4B6

SOLID STATE DEVICES AND CHEMICAL / BIOLOGICAL SENSORS

Answer not more than three questions.

All questions carry the same number of marks.

The approximate percentage of marks allocated to each part of a question is indicated in the right margin.

There are no attachments.

STATIONERY REQUIREMENTS

Single-sided script paper

SPECIAL REQUIREMENTS

**Engineering Data Book**

CUED approved calculator allowed

You may not start to read the questions printed on the subsequent pages of this question paper until instructed that you may do so by the Invigilator

1 (a) With reference to a metal-insulator-silicon (MIS) structure in which the semiconductor is p-type silicon, explain what is meant by (i) accumulation, (ii) depletion, and (iii) inversion. Illustrate your answer with appropriate electron energy vs distance band diagrams.

[30%]

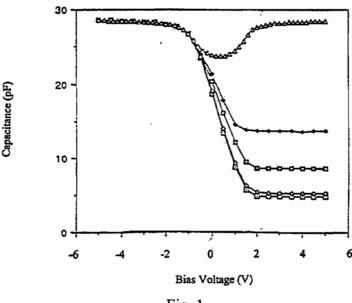

(b) Explain how small-signal capacitance vs voltage measurements are used to obtain electrical information about the properties of the MIS structure. Explain what is meant by small-signal measurement. Figure 1 shows the partially labelled results of measurements of small-signal capacitance versus voltage curves for a MIS structure, with the different curves corresponding to various levels of illumination intensity of the sample with white light. The x-axis denotes the dc voltage applied to the metal with respect to the semiconductor. Explain whether the semiconductor is n-type or p-type, and use energy-band diagrams to explain why the MIS structure is particularly sensitive to light in certain bias voltage ranges. Would the measured capacitance depend upon the ac measurement frequency?

[30%]

(c) Taking the MIS capacitor area to be  $3 \times 10^{-8}$  m<sup>2</sup> and the relative permittivity of the insulator to be 6, use the data in Fig. 1 to obtain a value for the insulator thickness. If the relative permittivity of the semiconductor is 10, estimate the maximum depth of the depletion region in these measurements. Explain whether the semiconductor can be depleted to a greater depth.

[40%]

Fig. 1

2 (a) List the main requirements for a successful projection display technology. Compare and contrast the performance, cost and range of application of (i) thin film transistor driven liquid crystal displays (LCD), and (ii) digital micromirror displays.

[30%]

(b) Describe the mode of operation and construction of an array of micromirrors for display applications. Sketch a typical optical system for a micromirror projection display. Comment on any other emerging possible applications of micromirror array technology.

[30%]

(c) Describe the structure and the principle of operation of a transmissive twisted-nematic liquid crystal display. Outline the principles of operation of an active matrix liquid crystal display. Include a qualitative diagram of typical driving waveforms for a bi-level (black/white) display over at least two frames.

[40%]

3 (a) Explain what is meant by (i) polarization, and (ii) domains in ferroelectric materials. How can a non-volatile memory cell be made by incorporating a ferroelectric material into a field effect transistor (FET) type device.

[30%]

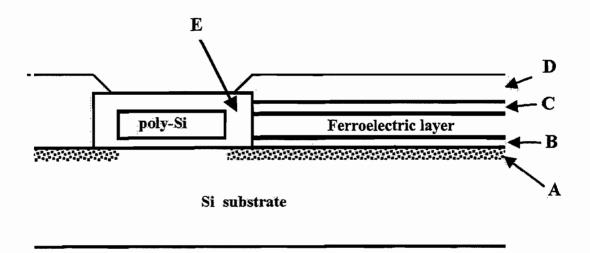

(b) Describe briefly how a one-transistor one-capacitor (1T/1C) ferroelectric memory cell operates with reference to the partial cross section in Fig. 2. Explain the functions of the layers A, B, C, D and E in Fig. 2, and describe the typical materials used for each layer. By using a charge vs voltage diagram and appropriate circuit diagram, explain how a memory cell can be addressed for a WRITE operation.

[40%]

(c) What is the typical performance of currently available ferroelectric integrated memory devices? Comment briefly on the performance comparison with other competing main memory technologies, and list the technology challenges which are outstanding for ferroelectric memory.

[30%]

Fig. 2

4 (a) Compare and contrast the performance and characteristics of field effect transistors having a channel made of (i) single crystal silicon, (ii) polycrystalline silicon, and (iii) amorphous silicon.

[30%]

(b) Outline a typical fabrication sequence used to produce amorphous silicon thin film transistors (TFTs) suitable for driving a liquid crystal display. Identify the steps in the process which are critically important in achieving high yield.

[40%]

(c) Discuss the range of applications of polycrystalline silicon TFTs and amorphous silicon TFTs with particular reference to computer displays.

[30%]

5 (a) Explain briefly what is meant by a MOS based chemical sensor, taking a hydrogen ChemFET as an example. Include in your answer an energy band diagram.

[30%]

(b) Explain briefly what is meant by a biosensor, taking an ion-sensitive field effect transistor (ISFET) as an example.

[30%]

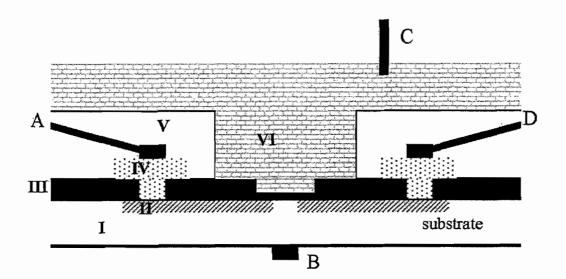

(c) Describe the construction of the ISFET shown in cross section in Fig. 3, and identify the electrical functions of the layers I, II, III, IV, V and VI. Explain the critical steps in the device fabrication process. Describe the mode of operation and the functions of the electrical connections to A, B, C and D.

[40%]

Fig. 3

## END OF PAPER