# 2007 IIB 4B2 Dr F Udrea fu@eng.cam.ac.uk

### Answers:

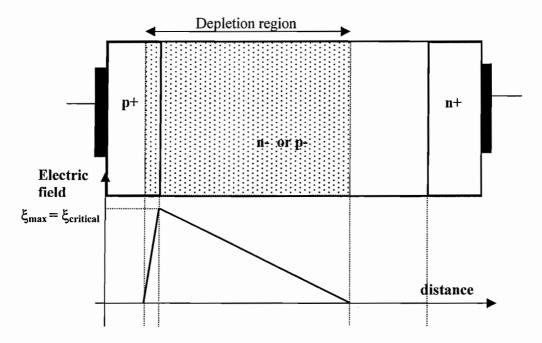

1. (a) The Non punch-through (NPT) high voltage diode is a based on a PIN diode where the thickness (width) of the lowly doped layer (n- or p-) is larger than the depletion region thickness (width) at breakdown. Thus the depletion region never reaches the n+ cathode region.

The Punch-through (PT) high voltage diode is a based on a PIN diode where the thickness (length) of the lowly doped layer (n- or p-) is smaller than the depletion region thickness (length) at breakdown. Thus the depletion region reaches the n+ cathode region before avalanche breakdown takes place.

For the MOSFET the NPT design is more appropriate. Although the drift length is shorter in the PT design, the NPT offers higher doping for the same breakdown voltage. The ratio between the doping and length of the drift region is higher in the NPT than in the PT design leading to smaller on-state drift resistance in the NPT case.

[30%] Pon = I S VI df = I d.t [Voktot +Rdf] dt

where d is the bomp of the convet growth in time L. Ipech Por = S Tpeak Voltzett dt + S (Tpeak)2. R & ddt I peoh , Voltant D + I peoh R D =  $16 \cdot 1.5 \cdot \frac{1}{2} + \frac{16^2 \cdot \frac{1}{2}}{2} \cdot \frac{1}{2} = \frac{27.32}{}$ Ptww.-1+ = E . d = 3.10-3.50.103 = 150 W The svitary losses ove much higher that he switching on - Thate losses indicating that he switching frequency is too high. I should be even-1 to kHz Lv a move r20/17 Solonces system

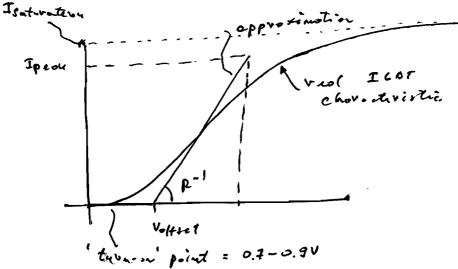

In an IGBT the turn-on' point in the on-state is likely to be around 0.7-0.9 V. That is ssmaller than Voffset which is 1.5 V. So at low currents, the approximation is likely to overestimate the voltage drop on the IGBT. The approximation is based on a linear increase in the current with the voltage beyond the offset voltage. In reality, as the device heads towards the saturation, the characteristics become sub-linear and the approximations is likely to underestimate the voltage drop on the IGBT. We also make the assumpations that the peak current Ipeak is greter than the saturation current.

So if the SMPS peak on-state current is much lower, when compared to the saturation current of the IGBT, it is most likely that the approximation will overestimate the on-state voltage drop in the IGBT. A practical device would therefore have lower on-state losses than those predicted by using eq. 1.

On the opposite, if the peak current is close to the saturation current of the IGBT the approximation will underestimate the on-state voltage drop in the IGBT. A practical device would therefore have much higher on-state losses than those predicted by using eq. 1.

#### 2. (a)

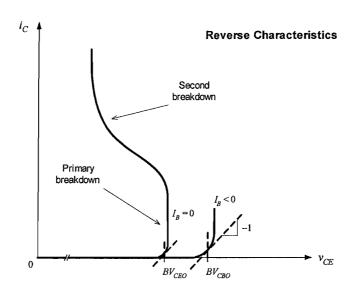

• Second breakdown is characterized by a snap-back in the breakdown characteristics. Second breakdown appears at large currents and results in a fast drop in the collector-emitter voltage. As the current increases, the temperature increases. If the temperature increases the injection is stronger and the current increases again. Hence BJTs suffer from a positive current-temperature feedback. This is known as thermal runaway. The thermal runaway is usually a local effect and leads to creation of hotspots.

[30%]

(b) The superjunction effect is based on multiple junctions disposed in the drift region with alternate layers of relatively highly doped n and p layers. The drift region is therefore made of thin n/p stripes rather than a single n- layer. The depletion of the drift region is in this case dictated by these n/p multiple junctions rather than by the classical p+/n- junction. Since the stripes are very thin (compared to their length), they deplete at much lower voltage (due to the extension of the depletion region across the n/p junctions). The net advantage is a major reduction in the on-state resistance for the same breakdown capability.

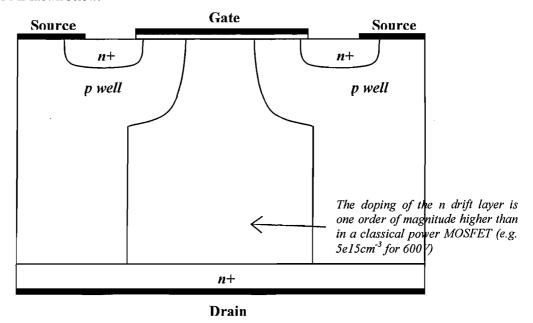

The Cool MOS is shown below:

The Cool MOS is base on superjunction effect. The on-state conduction area is limited to the n-stripe, but its doping is around one order of magnitude higher than in a classical MOSFET, leading to a factor of 5 reduction in the on-state resistance.

• The device has a limited breakdown range (300 – 1 kV), because at very low voltages, the channel resistance tends to dominate the overall resistance. A trench solution at such voltages would be more appropriate. At higher voltages ( above 1 KV), IGBTs, tend to be more efficient in terms of performance and cost. Also above 1 kV, the technological implementation of the n/p pillars in the drift region becomes extremely difficult.

[30%]

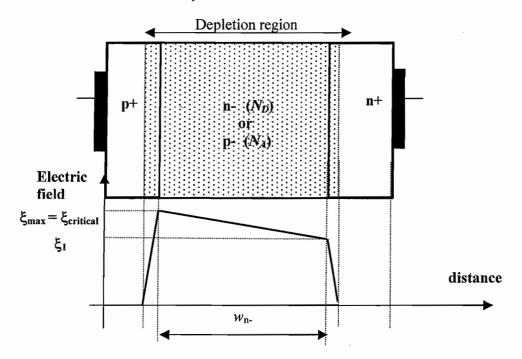

(c) To minimize the on-state resistance an NPT design should be used with the electric field at breakdown should just 'touch' the n+ drain contact region. Therefore the drift width  $W_d$  should equate  $W_{critical}$ .

3. (a) The  $dI_F/dt$  condition appears during the turn-on of the thyrsitor. If the rise time is too short ( $dI_F/dt$  is too high), the plasma cannot spread fast enough from the edge of the cathode (in the proximity of the gates) to the middle of the cathode. Therefore during the risetime the device conduction is limited to a small area around the edge (compared to the cross-sectional area of the device) and the voltage cannot fall quickly enough. Hence, large instantaneous power dissipation occurs during this period of time which leads to hot spot formation followed by thermal runaway and eventually permanent failure.

Two ways to improve this:

- increase the density of gates per total area that is to say that we increase the density of gate-cathode inderdigitation. This also has the advantage of shortening the turn-off time (as well as the turn-on time).

- use a smaller auxiliary or pilot thyristor integrated on the same silicon chip with the

main thyristor. The current injected into the gate of the pilot thyristor is relatively

small but this is amplified by the pilot thyristor so that the gate current delivered to

the main thyristor is relatively high

[30%]

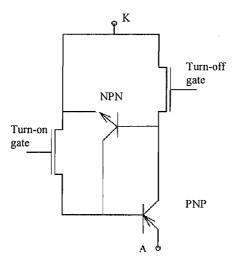

- (b) The MCT has a very low on-state resistance, similar to that of GTO thyristors.

- In comparison with the GTO thyristor, the MCT can be turned on and off using a high input impedance MOS gate.

- In the off-state the device behaves similarly to a thyristor with most of the voltage supported across the n- drift region. As with the thyristors, the device breaks when the sum of the current gains of the NPN transistor and PNP transistor reaches 1.

- The device is turned on by applying a positive voltage on the gate, thus allowing injection of electrons into the n- base.

- The current flow in the on-state occurs through the two coupled bipolar transistors (as shown on the equivalent circuit). As a result of high conductivity modulation specific to thyristor structures, the n- base resistance is reduced significantly.

- The turn-off of the MCT is achieved by short-circuiting the base (p base) -emitter (n+cathode) junction of the NPN transistor (component of the thyristor structure) through a pMOS channel. To accomplish forced gate turn-off, the p-channel resistance should be so low as, when all the hole current is diverted via the p-channel MOS structure, the forward-bias of the n+ cathode/p base junction to remain below 0.5 V (the threshold voltage of the junction). However, due to non-uniform current distribution from cell to cell, hot-spot formation and the significant reduction of the cathode junction threshold voltage at high temperatures, the maximum controllable current density that satisfies the above condition is very low.

[30%]

# Compared to IGBT

Advantage: The MCT offers lower on-state resistance – characteristic to thyristors ( heavy injection of plasma from both sides of the drift region)

## Disadvantages:

- Complex structure & high cost

- Filamentation effect. Negative temperature coefficient can lead to hotspot formations

- No on-state control of the current ( no MOS current saturation)

- Lower breakdown voltage for the same doping and drift length compared to an IGBT (the device breaks via breakover mechanism rather than avalanche)

[10%]

4. (a) The turn-off process is based applying a reverse-baised voltage set by an external circuit for a minimum period of time. Initially the currents starts to decrease, but plasma is still present in the dvice (as this may take a long time to clear). The current becomes negative, while the plasma is decaying. At the end of this period, the plasma is removed allowing a depletion region to be formed. The reverse voltage is now fully applied to the device, while the negative current starts to decrease to zero. After the current is completely zero, a forward blocking voltage can be applied with a dV/dt ramp. The ramps should be carefully chosen as this introduces a displacement current C depl dV/dt. If this current is greater than the breakdover current, the transistor turns-on again (fails to turn-off).

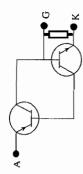

To minimise the effect of the displacement current cathode-shorts or anode-shorts can be introduced. These shorts lower the current gains of the NPN and PNP transistor respectively, increasing the breakover current and absorbing some of the un-wanted displacement currents. The equivalent circuit of the thyristor showing cathode-shorts is given below, where a resistance is placed between the emitter and the base of the NPN transistor.:

For anode shorts the equivalent circuit is similar, with the short resistance placed between the anode and the base

Equivalent circuit of a thyristor with cathode shorts.

[30%]

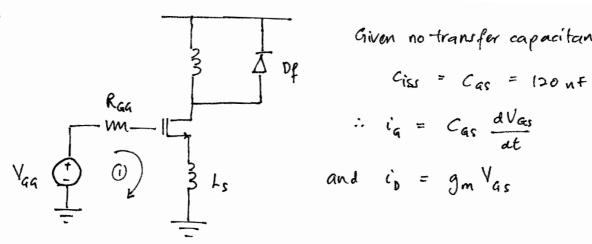

Given no transfer capacitance,

Along loop 0,

$$V_{AG} = i_{G}R_{GG} + V_{GS} + L_{S} \frac{di_{S}}{dt}$$

$$= i_{G}R_{GG} + V_{GS} + L_{S} \frac{d}{dt} (i_{D} + i_{G})$$

$$= C_{GS}R_{GG} \frac{dV_{GS}}{dt} + V_{GS} + L_{S} \frac{d}{dt} \left\{ g_{m}V_{GS} + C_{GS} \frac{dV_{GS}}{dt} \right\}$$

$$= V_{GS} + \frac{dV_{GS}}{dt} \left\{ R_{GG}C_{GS} + g_{m}L_{S} \right\} + \frac{d^{2}V_{GS}}{dt^{2}} L_{S}C_{GS}$$

laking Laplace,

$$\frac{V_{as}}{s} = V_{as} \left\{ 1 + \left( R_{as} C_{as} + g_m L_s \right) s + L_s C_{as} s^2 \right\}$$

$$\frac{V_{GG}}{S\left(S+\frac{1}{T_{1}}\right)\left(S+\frac{1}{T_{2}}\right)} \qquad \begin{array}{l} R_{GG}C_{GS}=3.3\times120n=396n\\ 9mLs=600\times2n=1200n\\ L_{S}C_{GS}=2n\times120n=240n^{2} \end{array}$$

Solving for I, and Iz,

$$T_1, T_2 = -\left[ \frac{-1596 n \pm \sqrt{(1596n)^2 - 4(240n^2)}}{2(240n^2)} \right]^{-1}$$

= 1595.8 ns, 0.150 ns too small!

Hence, taking the inverse laplace on  $(x) \Rightarrow V_{qs}(t) = V_{qq} \left[1 - \exp\left(-\frac{t}{4}\right)\right]$ .

Hence,

$$i_s(t) = g_m V_{qs}(t)$$

$$= g_m V_{qq} \left[ 1 - \exp\left(-\frac{t}{L_t}\right) \right].$$

$$\Rightarrow \frac{di_0(t)}{at} = \frac{g_m V_{aa}}{T_1} \exp\left(-\frac{t}{T_1}\right).$$

At t=0, initial decrease in current:

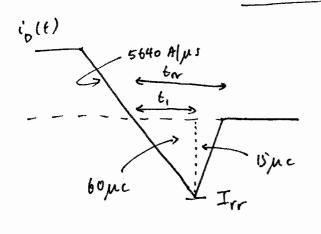

$$\frac{di_0(t)}{at}\Big|_{t=0} = \frac{(6005)(150)}{(1595.805)} = \frac{5640}{40} = \frac{1}{10}$$

Approximating

$$\frac{di_0(t)}{dt}$$

to be linear,

$$\int_0^t \frac{di_0(t)}{dt} \Big|_{t=0}^t t dt = 60 \mu C$$

$$\therefore t_1 = \int \frac{2 \times 60 \mu C}{5000 \text{ Alws}}$$

Assuming linearity,

$$t = 2 \times 15 \mu c$$

$$t_{rr} = \frac{2 \times 15 \mu c}{823 A} + t_1$$

$$\Rightarrow I_{rr} = \frac{di_{p}(t)}{dt}\Big|_{t=0} \cdot t,$$

= 145.9ns