# ENGINEERING TRIPOS PART IIB

Wednesday 27 April 2011 2.30 to 4

Module 4M6 - ANSWERS

# DR A J FLEWITT

# 4M6: MATERIALS AND PROCESSES FOR MICROSYSTEMS (MEMS)

2

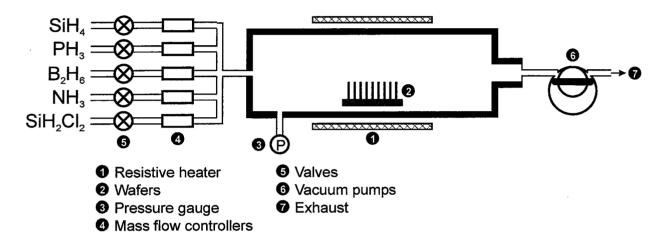

1 (a) Silicon nitride has become a mainstay of the MEMS industry and is frequently deposited by low pressure chemical vapour deposition (LPCVD). A schematic diagram of an LPCVD system is shown below:

Fig. 1

A mixture of  $SiH_2Cl_2$  and  $NH_3$  is fed into a chamber at a pressure of ~70 Pa. The substrates, which are stacked vertically, are heated at ~800° C, which is sufficient to thermally induce a chemical reaction on the surface of the substrate forming a-SiN by

$$3SiH_2Cl_2 + 4NH_3 \rightarrow Si_3N_4 + 6HCl + 6H_2$$

Stoichiometric LPCVD a-SiN produced with a SiH<sub>2</sub>Cl<sub>2</sub>:NH<sub>3</sub> flow ratio of 1:10 suffers a high tensile stress. However, material which is stress free or even compressive can be produced by increasing the silicon content of the nitride. A SiH<sub>2</sub>Cl<sub>2</sub>:NH<sub>3</sub> flow ratio of 1:6 is found to produce stress-free material.

[35%]

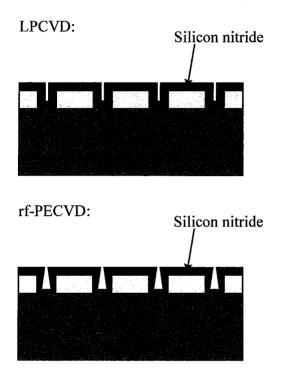

(b) The cross section for LPCVD and rf-PECVD depositions are shown in Fig. 2:

Fig. 2

In the case of LPCVD, deposition is limited by the chemical reaction taking place at the material surface (reaction limited). Therefore, deposition scales linearly with area, and conformal coating results, leaving a uniform, pinhole-free surface. However, rf-PECVD is transport limited, and there is limited supply of species to sidewalls and surfaces in trenches, resulting in a non-conformal coating.

[25%]

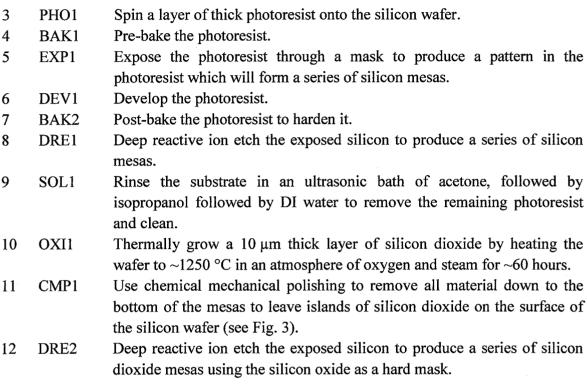

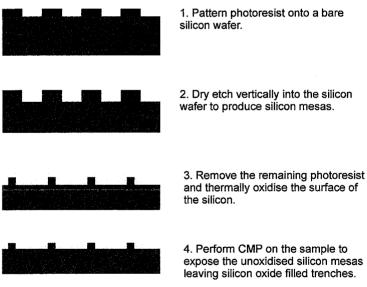

## (c) The process flow is as follows:

| Step | Code | Description                                                                                                              |

|------|------|--------------------------------------------------------------------------------------------------------------------------|

| 1    | RCA1 | Boil a silicon substrate in RCA Clean 1 (NH <sub>3</sub> (aq):H <sub>2</sub> O:H <sub>2</sub> O <sub>2</sub> ) to remove |

|      |      | organic contaminants.                                                                                                    |

| 2    | RCA2 | Boil a silicon substrate in RCA Clean 2 (HCl:H <sub>2</sub> O:H <sub>2</sub> O <sub>2</sub> ) to remove                  |

|      |      | metallic ion contaminants.                                                                                               |

Version 2

Fig. 3

[Examiner's note: Many student opted to use a bHF dip rather than the DRIE. This will lead to significant undercutting of the oxide layer and sidewalls that are not vertical, as required in the design.]

The tolerance in the horizontal dimensions of the mesas is likely to be limited by the photolithography (typically ~0.5  $\mu m$ ) coupled with the verticality of the DRIE. This normally achieves verticality of  $\pm 1^{\circ}$ , which is equivalent to ~0.2  $\mu m$ . Vertical depth will be limited by the ability to maintain a 10  $\mu m$  thick silicon dioxide deposition. This can be checked optically. The ability to control the CMP and second DRIE will also affect the trench depth.

# Gammer's comment

This question examined the students' understanding of chemical vapour deposition prceses for thin film materials and their ability to construct a simple process flow for the fabrication of oxide mesa structures. Most candidates generated a good process flow, but failed to mote that vertical sidewalls were required for the mesas, and so used an overly simple process flow.

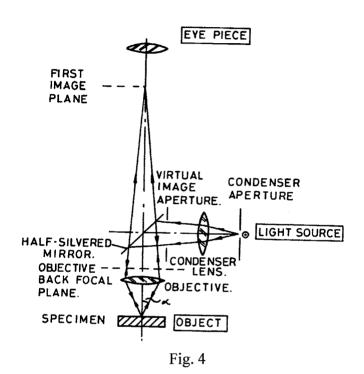

2 (a) A schematic diagram of an optical microscope is shown in Fig. 4.

A light source is used to shine light into the system through an aperture. The light is then collimated by a condenser lens and is then reflected from a half-silvered mirror onto the objective lens, which focuses the light onto the sample, placed a short distance (a few mm) below). Light that is reflected from the surface of the sample is then collected by the objective and passes through the eye-piece lens for viewing.

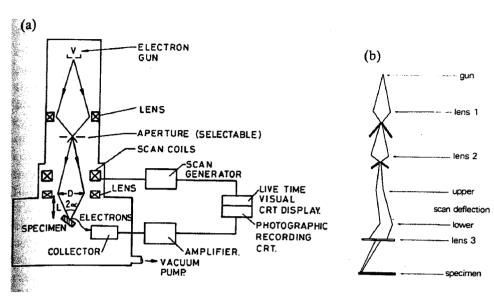

The scanning electron microscope is shown in Fig. 5.

Fig. 5

In this case, electrons are produced by an electron gun, and focused through an aperture by an electrostatic lens. A second set of coils are then used to focus and scan the electron beam over the sample surface. Reflected electrons are then collected and amplified to produce a signal which can be turned into an image on a screen.

In the case of optical microscopy, resolution is limited by diffraction of light through the finite aperture size of the objective lens. As diffraction depends on the wavelength of light, this means that resolution is limited to be of the order of the wavelength of light (i.e.  $\sim$  1  $\mu$ m).

In the case of electron microscopy, diffraction again limits resolution, but as the wavelength of the electron (given by the de Broglie relation) is very much smaller than for light, then the resolution of the SEM is significantly better then for optical microscopy.

[30%]

(b) Optical microscopy is very helpful for MEMS visualization as it is non-destructive and very simple to implement. Furthermore, most MEMS devices have a minimum feature size that is rather greater than 1  $\mu$ m, and so the limited resolution of optical microscopy is not a major limitation. The limited depth of focus also allows vertical depths to be roughly measured by adjusting the focus so that different layers of a structure

are sharp, and then measuring the change in height of the objective lens. However, the limited depth of focus is also a major limitation as whole MEMS structures usually cannot be visualized at the same time.

Electron microscopy has a much greater depth of focus, and so whole structures can be imaged. Greater magnifications can be achieved with electron microscopy, allowing the structural detail from fabrication to be seen. It is also, generally, a non-destructive technique. However, it requires expensive equipment, and the sample must be placed under vacuum for imaging. Also, insulating surfaces must usually be coated in gold to allow imaging without charging.

The image in Fig. 2 of the exam paper was obtained by SEM. This can be determined from the excellent resolution down to the sub-micron level and from the great depth of focus, which would not be possible by optical microscopy.

[30%]

(c) (i) The nickel layer is clearly of the order of micron in thickness. Evaporation and sputtering are rarely used for such thick layers due to the slow growth rate. Also, the substrate is silicon, and therefore conductive. Electroplating is therefore the most likely growth technique.

[20%]

(ii) Such curvature indicates that there must be a stress gradient in the material, with the upper layer originally being under compressive stress with respect to the lower. With electroplating, it is known that the concentration of the plating solution changes during deposition and a change in the density of the nickel due to changes in deposition rate and concentration would probably cause this effect. Also, changes in the temperature of the plating solution (particularly heating during deposition) would also produce a stress gradient.

[20%]

#### Version 2

This question examined the students' understanding of different types of microscopy for imaging MEMS devices. It then proceeded to get the students to study the image of a MEMS device and comment on the origin of deformation in the device structure and how this might have arisen given the material that the device was fabricated from.

3 (a) If an etch process has been well characterized, then it should be possible to produce etched featured of a well-defined depth. However, in practice etch rates vary with time due to concentration changes, and wetting and de-wetting mean that precise time etching of wet etches is difficult. Therefore, a means of suddenly reducing the etch rate at a certain depth can be employed to ensure that a particular quantity of material is removed, and this is known as an etch stop. The advantage is that features of precise depths may be produced, but the disadvantage is that there is an increase in process complexity as the etch stop must be incorporated.

There are a number of techniques for producing an etch stop:

# · Dielectric etch stop

- Dielectrics, such as silicon nitride, tend to have a reduced etch rate compared to silicon

- A layer may then be introduced underneath the layer to be etched to ensure that the etch terminates at the correct depth

# • Doping selective etching (DSE)

- Silicon which has been heavily doped with boron to a concentration of  $\sim 10^{26}$  m<sup>-3</sup> has a significantly reduced anisotropic etch rate

- Therefore, an etch of a low doped p-type or n-type silicon layer will naturally halt on a heavily boron doped layer, resulting in a very smooth surface

- However, the addition of boron tends to cause a significant intrinsic stress in the silicon, which limits the use of these layers as mechanical components

#### • Bias selective etching (BSE)

- This is otherwise known as an electrochemical etch stop

- A positively biased silicon wafer will be oxidised in an etchant solution to form a protective oxide layer which will prevent etching

- A current is required for the oxide to form, therefore, a reverse biased pn junction in the solution will not be able to form a passivation layer until all of the p or n-type material has been removed

- At this point a current may flow, and the silicon surface will quickly oxidise, stopping the etch at the change in doping density

[25%]

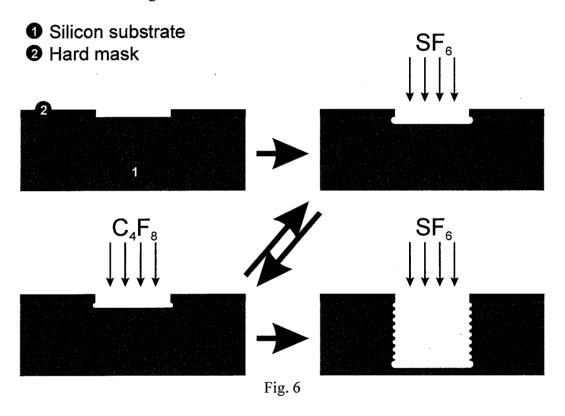

(b) In the first stage of the BOSCH process, a dense  $SF_6$  plasma is used to etch a thin layer of silicon. In the second stage, a  $C_4F_8$  plasma is used to deposit a thin fluorine polymer on the etched surface. When  $SF_6$  is reintroduced, it preferentially removes the polymer from the bottom of the etch structure, exposing the silicon in this region and allowing the etch to proceed. The sidewalls, however, remain protected and are not etched. This is summarised in Fig. 6.

Standard RIE tends to produce etch rates between 10 and 100 nm min<sup>-1</sup>. Whilst this is sufficient for surface micromachining, it is far too slow to allow a layer hundreds of  $\mu m$  thick to be etched, whereas DRIE allows etch rates up to  $\sim\!20~\mu m$  min<sup>-1</sup>. Furthermore, greater anisotropy can be achieved with DRIE compared with RIE.

(c) The tolerance requirement in width will require DRIE to form the microfluidic channels and an etch stop will be required to meet with vertical dimension tolerance over a whole wafer. Therefore, a suitable process flow would be as follows:

| Step | Code | Description                                                                                                          |

|------|------|----------------------------------------------------------------------------------------------------------------------|

| 1    | RCA1 | Boil two silicon substrates in RCA Clean 1 (NH <sub>3</sub> (aq):H <sub>2</sub> O:H <sub>2</sub> O <sub>2</sub> ) to |

|      |      | remove organic contaminants.                                                                                         |

| 2    | RCA2 | Boil the two silicon substrates in RCA Clean 2 (HCl:H <sub>2</sub> O:H <sub>2</sub> O <sub>2</sub> ) to              |

|      |      | remove metallic ion contaminants.                                                                                    |

| 3    | OXI1 | Thermally grow a 2 µm thick layer of silicon dioxide by heating the wafer                                            |

|      |      | to ~1250 °C in an atmosphere of oxygen and steam on one of the two                                                   |

|      |      | wafers.                                                                                                              |

| 4    | HYD1 | Plasma hydrophilise the surface of the two wafers.                                                                   |

| 5    | FUS1 | Fusion bond the two wafers and anneal at 1000 °C (this creates a buried                                              |

|      |      | silicon dioxide layer for an etch stop).                                                                             |

| 6    | CMP1 | Chemical mechanical polish back the top Si wafer to a thickness of                                                   |

|      |      | 100 μm.                                                                                                              |

| 7    | SIN1 | Deposit a thin (~200 nm) layer of silicon nitride onto the surface of the                                            |

|      |      | un-oxidised wafer by LPCVD to act as a hard mask.                                                                    |

| 8    | PHO1 | Spin a layer of photoresist onto the glass layer.                                                                    |

| 9    | BAK1 | Pre-bake the photoresist.                                                                                            |

| 10   | EXP1 | Expose the photoresist through a mask to produce a pattern in the                                                    |

|      |      | photoresist which is a track of 10 μm across.                                                                        |

| 11   | DEV1 | Develop the photoresist.                                                                                             |

| 12   | BAK2 | Post-bake the photoresist to harden it.                                                                              |

| 13   | RIE1 | Remove the exposed silicon nitride by reactive ion etching using SF <sub>6</sub> to                                  |

|      |      | expose the channel areas leaving the silicon nitride as a hard mask for the                                          |

|      |      | DRIE.                                                                                                                |

| 14   | DRE1 | Deep reactive ion etch the exposed silicon down to the silicon dioxide                                               |

|      |      | etch stop using the BOSCH process.                                                                                   |

| 15   | SOL1 | Rinse the substrate in an ultrasonic bath of acetone, followed by                                                    |

|      |      | isopropanol followed by DI water to remove the remaining photoresist                                                 |

|      |      | and clean.                                                                                                           |

Remove the remaining silicon nitride by reactive ion etching using SF<sub>6</sub>.

[50%]

[Examiners' note: Many students opted to use just a single Si wafer. This means that you cannot control the depth of the etch of the channels accurately using the etch stop, which is possible by effectively creating an SOI wafer by bonding two together.]

This question examined the students' understanding of the use of etch stops in the fabrication of MEMS devices. The students then had to describe how deep reactive ion etching works, and concluded with the students integrating these two together in a process flow for the production of microfluidic channels on the surface of a silicon wafer. The process flow really required the use of two silicon wafers that were bonded together in order to obtain the required tolerances on device dimensions. Only one student actually did this, with the others preferring to use a single wafer and sacrifice some tolerance as a result.

4 (a) Biocompatibility must be considered when a MEMS device is to operate in contact with a biological system, means ensuring that there are no undesired reactions between the MEMS device and the biological system. This includes both effects of the MEMS device upon the biological system, such as cytotoxicity, genotoxicity, sensitisation, irritation, etc. and effects of the biological system upon the MEMS device, such as etching of materials or diffusion of impurities.

[15%]

(b) Other considerations may include:

## • Functionality

- Full biomicrosystems need to be carefully designed and properly partitioned

- We need to consider what really needs to be 'on chip' in the biological environment

- Frequently only static systems are required in which microwells are used to hold small volumes of material in place either electrically or microfluidically and detection is performed optically

- Some silicon electronics is frequently required to perform in situ preamplification of small electrical signals

### Optical detection

- Detection of biological molecules frequently relies on either microscopy or fluorescence

- In the case of microscopy, most objectives are designed for use with glass coverslips of 170  $\mu$ m thickness, and deviations in the thickness or refractive index from the standard can limit resolution

- In the case of fluorescence, it is important that photons of the required wavelength can enter and leave the system without significant scatter (such as that due to surface roughness) and that the system will not itself fluoresce (SU8 is a problem in this regard)

### • Cost and disposability

- Low cost, disposable devices can open up large markets, as high cost sterilisation is not necessary and cross contamination of samples is avoided

- Low cost is achieved through the use of cheap materials and processes

#### • Sterilisation

Sterilisation is the destruction of all biological life (and so is NOT the same as cleaning)

- Materials in bioMicrosystems must be able to withstand one of the following sterilisation techniques

- Heat sterilisation in a autoclave (121° C, >10 psi for >30 minutes in either steam or dry heat)

- Gas sterilisation (ethylene oxide ambient temperature, 30-60% relative humidity for >16 hours) [NOTE: ETO is carcinogenic and toxic so this method is far from ideal]

- Liquid disinfection (chlorine, iodine, 50-70% aqueous ethanol or isopropanol)

- UV sterilisation (254 nm, 40 μW cm<sup>-1</sup>) [NOTE: not technically sterilisation, but will reduce the number of micro-organisms]

[45%]

(c) Microcontact printing utilizes a PDMS stamp to pattern a biological material on a surface with resolution down to the nm level:

1 The PDMS stamp is coated in the hydrophilic or hydrophobic end of alkane thiol 1.

2 The coated stamp is pressed onto the substrate to be coated (such as gold coated silicon).

3 The PDMS stamp is removed, leaving alkane thiol 1 only at the contact points.

4 The sample may now be exposed to a second alkane thiol which will only be able to coat the exposed regions of the substrate.

[20%]

(d) The process flow for producing a PDMS stamp is as follows:

- 1 Photoresist is patterned onto a silicon substrate in the negative of the pattern to be printed. The surface is then treated with (tridecafluoro-1,1,2,2-tetrahydrooctyl)-1-trichlorosilane to reduce adhesion.

- 2 PDMS (polydimethylsiloxane) is spin coated over the patterned resist and cured at 60° C for one hour.

- 3 Finally, the PDMS may be simply peeled away from the substrate to leave the printing stamp.

[20%]

This question examined the students' understanding of the issues that arise when designing a MEMS device for biological applications. This was a very well answered question which showed that the students had gained a thorough understanding of the issues involved.