1. (a)

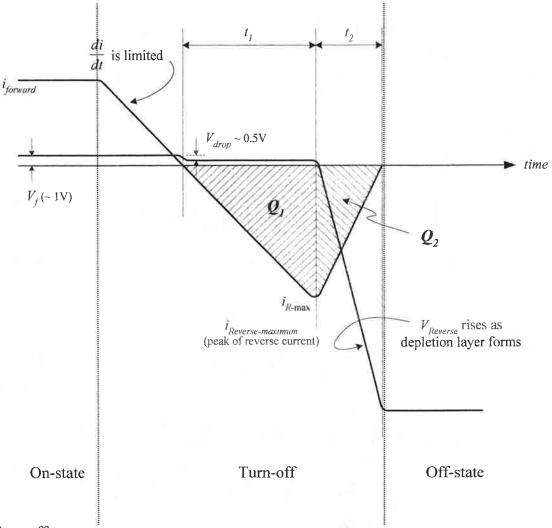

Turn-off

- di/dt is limited by the external circuit. As an attempt is made to reverse-bias

the diode, the current starts decreasing and flows in the opposite direction as

plasma is still present.

- $Q_I$  is associated with the plasma in the drift region and  $t_I$  is the time taken to remove it.

- Once plasma is removed at the end of  $t_I$ , a depletion region starts to grow and the reverse voltage across the diode can increase. At the end of this region the device can block the voltage and the current decreases to a leakage level.

[36]

(b) The device is an IGBT. The turn-off features a first fall, associated with the drop in the electron current (as the channel (MOS inversion layer) is suppressed) and the second drop is usually associated with the hole sweep out and recombination of plasma. This takes a longer time to remove.  $I_h$  is approximately equal to the original hole current at the cathode side (as the electron current drops very fast when the channel is 'killed').

(2/2)

(b) (ii)

$$T = \frac{1}{\sqrt{3}} = \frac{1}{100 \text{ kH}_2} = 10 \text{ hs}$$

$$D = 50 \text{ low} = 5 \text{ low} =$$

TULLY -ON COUSES = 24 + 4,01 W = 6.03 M 1,41W Cosses = TURH - > FF LOSS E) = 0.03 + 6.05 + 2.6 + 3 = OH -STATE o w COSSES = OFF - STATE = 11. C&W

= 1.41 + 6.03 + 11.68 = 19.12W TOTAL

[50%]

2.

## (a) Curvature effect

The shape of the junction which supports the voltage plays an important role in 'field crowding'. The higher the radius of a cylindrical or spherical junction the closer the breakdown is to that of an ideal parallel-plane junction. However, in most microelectronics processes the junction depth is limited to a couple of microns up to maximum 10-15 microns. The curvature effect can be reduced in multiple cell power devices such as MOSFETs or IGBTs by placing the cells (with multiple junctions) close together to simulate almost a 'continuous junction'. By solving Poisson's equation for a cylindrical junction one can show that the maximum electric field for the same reverse voltage applied increases significantly compared to that in a planar junction.

## Edge breakdown

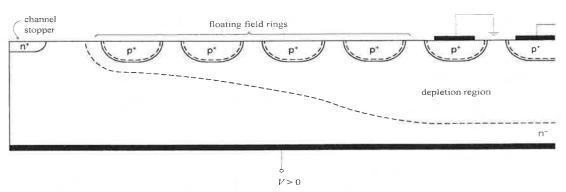

Placing cells very close together has only limited value because at the edge there is always a last cell left 'unprotected'. Premature edge breakdown is a very common effect in power devices. For this, special techniques can be used.

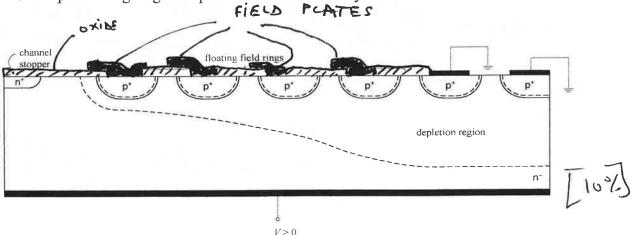

A good termination technique is the floating field ring technique. This is based on distributing the field between highly doped p+ floating field rings to alleviate the edge effect.

A similar result can be obtained with the junction termination extension. This is based on having regions of lowly doped p- layers spread out uniformly the electric field at the edge of the device. The p- layers have to be depleted at breakdown.

The field plates placed on each ring help to reduce the electric field at the surface of each of the p+ floating ring. The position is schematically shown below:

(a) L

72.

[20%]

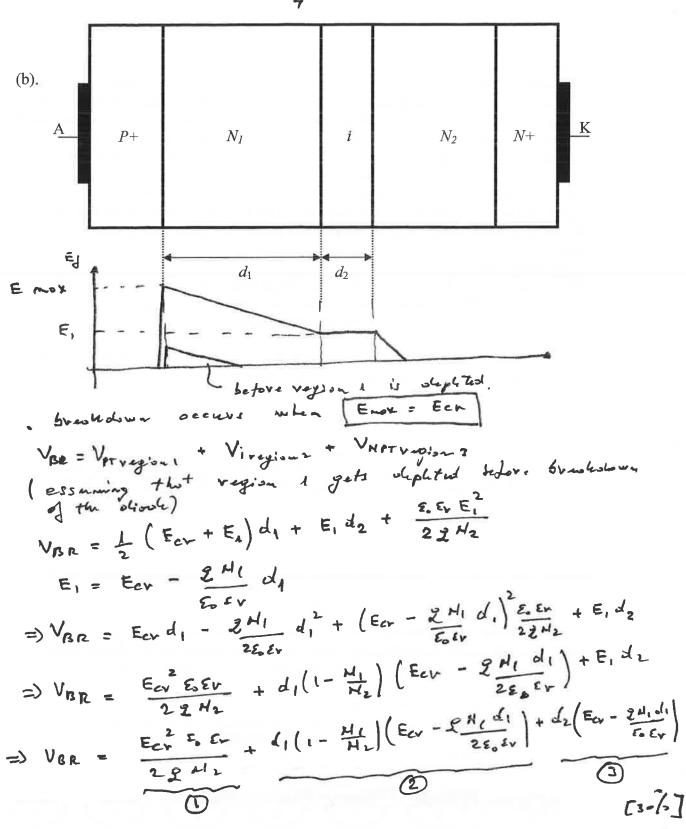

id H, > M2 (2) is hypetime =) Von dievens

2 Nz H ij Es positive => Vou l'acreons 51 HI4 K MIL [20%] oli (111) cs 2 3 is motion Mi N 1010 cm 2 (intrinsic corrier VBR = Ecr (d, + d) + Ecv Eo Er 22 Hz this fr. Born 5 (3) Ecr [20/3] **X**. 0/1

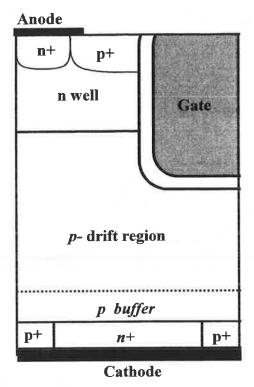

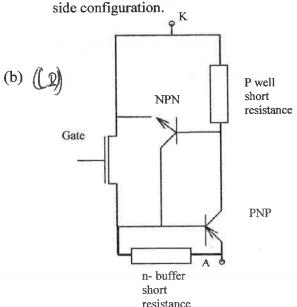

The p+ shorts are connected together with the n+ electron emitter to the cathode terminal. The device could be used in the high side with the anode as high voltage terminal. It features a p-channel and p-drift region. When the gate is negative with respect to the anode and the inversion layer is formed, holes can travel from the p+ anode through the channel to the p-drift region and are collected by the p+ shorts. Once the n+/p buffer junction becomes

drift region and are collected by the p+ shorts. Once the n+/p buffer junction becomes forward biased, electrons are injected from the n+ emitter into the p-drift region and via the action of the npn transistor as well as that of the PIN diode, conductivity modulation (formation of plasma) takes place in the p-drift region resulting in low on-state resistance. The

turn-off process is fast, as the npn transistor is weak (due the shorts) resulting in less plasma and additionally the shorts can collect holes during the turn-off process.

• Compared to a p-channel IGBT, the cathode-shorted p channel IGBT features a snapback (due to the transition from a unipolar device to a bipolar device). However it is expected to be faster with lower turn-off losses (see above for the reason).

Compared to an anode-shorted n-channel IGBT, the cathode-shorted p channel IGBT has higher on-state losses due to higher channel resistance. The n-channel would operate in the low-side configuration while the p-channel would operate in the high

[20°/]

T30°6J

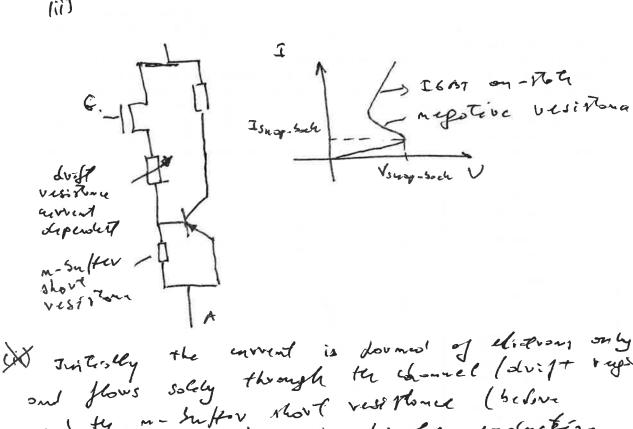

and flows solely through the channel (dvi)+ ruple and the m- Suffer, short vess Plance (belove The Sipolar constactés a the susp-bock). o ceurs only when the onde fruitin becomes formoust - Sisterd.

Ismp-beh. Ps = 0.70

=) Ismop book = 0.7 = 70 mm x

= (Reh + Rose + Edi-17 + Rspr) Ismog. Web +0.7V =

= 70.0.07 + 0.7 = 5.10

The voltage doop on the channel of the Somp- boch wirend (70m A) is 1.40 & Uz-by= 100 whole justifies that the Mos is in the cinor

(iii) Cotch - up will occur when drap In Rowal = 0,30 [30]  $=) I_A = \frac{0.7}{0.3 \cdot 1} = 2.33 A$

If the Temperature is voised then the voltage with 2mV/°C => 0.1V

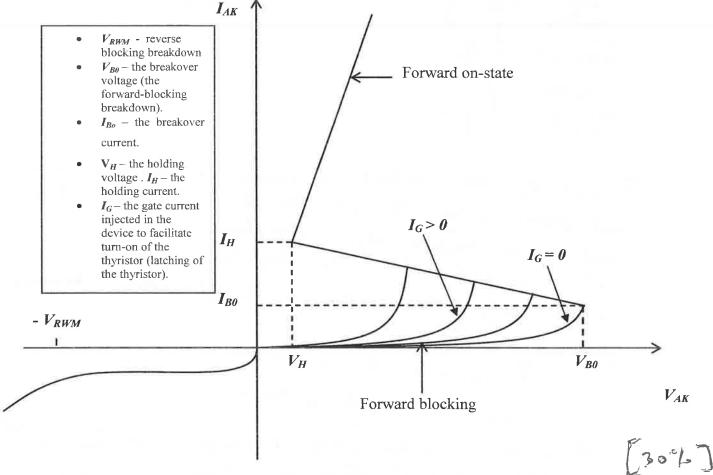

4 (a) **Symmetrical thyristors (NPT)** have both forward and reverse blocking capability. In the forward blocking state the anode is biased positive with respect to the cathode, while in the reverse blocking state the anode is biased negative with respect to the cathode. Symmetrical thyristors are based on a NPT junction design. The device has however reverse-blocking capability which can be of use in special power electronic circuits. In addition, these devices can be turned-off by reverse biasing the voltage between anode and cathode.

Aymmetrical thyristors (PT) have only forward blocking capability. They are based on a PT junction design and they feature a buffer between the n- drift region and the p-anode to make sure that no punch-through breakdown occurs. The lowly doped drift region is however fully depleted at breakdown. When compared to the symmetrical thrristors, the asymmetrical thyristors have thinner n-drift region and therefore reduced on-state and transient losses. Because they do not offer reverse blocking capability, they cannot be turned-off by reversing the anode-cathode voltage. For this reason most of the asymmetrical thyristors are GTOs or GCTs where the turn-off is accomplished via the gate.

(b) This effect is very severe during turn-off when a high forward voltage is re-applied to the structure. There is a maximum dV/dt rating above which the displacement current created through the junction capacitance will be greater than the breakover current, thus resulting in a parasitic re-turn-on (the device refuses to turn-off).

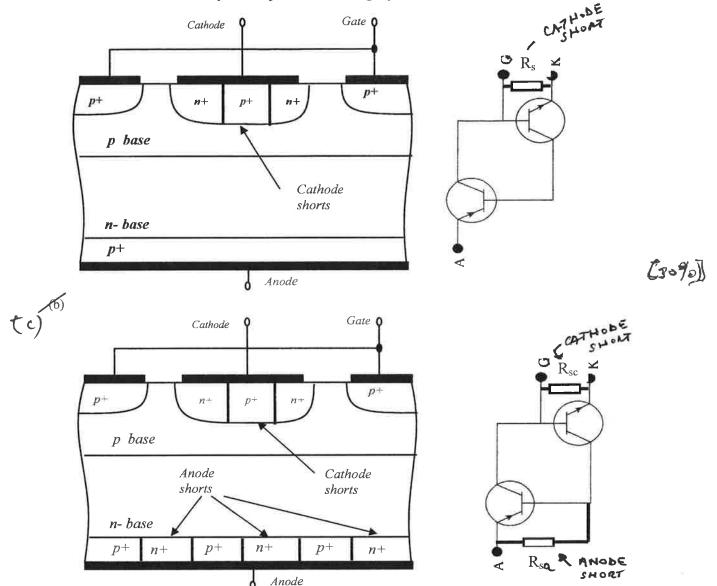

One solution to minimize the effect of the dV/dt (in other words, to increase the maximum dV/dt rating). The shorts can collect some of the displacement current which could otherwise turn-on the npn transistor. Since a large component of the displacement current is safely absorbed via the cathode shorts, the slope  $dV_F/dt$  can be higher without triggering the parasitic re-turn-on of the thyristor. The smaller the short resistance  $R_s$ , the more effective the cathode short is, and the higher the maximum  $dV_F/dt$  rating.

There are two more advantages resulting from the use of cathode shorts:

- (i) the increase in the breakover point this gets closer to the maximum breakdown (dictated by avalanche)

- (ii) a faster turn-off. This is due to lower plasma injection

There are however two major drawbacks:

- (iii) the turn-on is slightly slower (as the npn transistor is weakened by the shorts).

- (iv) The on-state losses are slightly higher as the npn transistor has lower gain and therefore the plasma injection will be slightly weaker.

The shorts would lower the gain of the pnp and npn transistors resulting in less plasma formation. The turn-off losses would be lower, but the device will be more difficult to turn-on. The presence of the anode shorts and cathode shorts leads to the formation of an anti-parallel diode (p+ shorts & pbase/n-base & n+). This diode prevents a reverse blocking voltage to be applied. Therefore the device cannot turn-off in a similar manner to a classical thryristor by applying a high reverse voltage between anode and cathode. The device can only operate as a GTO (or GCT) with the gate used for both the turn-on process (positive current pulse) and turn-off process (negative current pulse). The equivalent circuit would be that of a GTO with an anti-parallel PIN diode.

[40/5]

Note: The device combi also experience prosland of Mortmap whem the potentials on the hande and Cathodo ove zero and the gate is siosed. There is a povositie Pint diash between the gate and the enough which becomes forward - Staped.